## 8049H/8039HL HMOS SINGLE COMPONENT 8-BIT MICROCOMPUTER

- 8049H Mask Programmable ROM

- 8039HL CPU Only with Power Down Mode

- 8-BIT CPU, ROM, RAM, I/O in Single Package

- High Performance HMOS

- Reduced Power Consumption

- 1.4 usec and 1.9 µsec Cycle Versions All Instructions 1 or 2 Cycles.

- Over 90 instructions: 70% Single Byte

- 1K x 8 ROM 64 x 8 RAM 27 I/O Lines

- Interval Timer/Event Counter

- Easily Expandable Memory and I/O

- Compatible with 8080/8085 Series Peripherals

- Two Single Level Interrupts

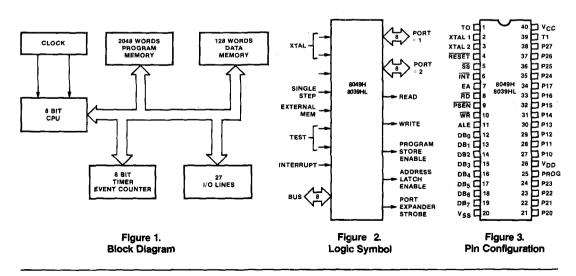

The Intel® 8049H/8039HL are totally self-sufficient, 8-bit parallel computers fabricated on single silicon chips using Intel's advanced N-channel silicon gate HMOS process.

The 8049H contains a 2K X 8 program memory, a 128 X 8 RAM data memory, 27 I/O lines, and an 8-bit timer/counter in addition to on-board oscillator and clock circuits. For systems that require extra capability the 8049H can be expanded using standard memories and MCS-80®/MCS-85® peripherals. The 8039HL is the equivalent of the 8049H without program memory and can be used with external ROM and RAM.

To reduce development problems to a minimum and provide maximum flexibility, a logically and functionally pin compatible version of the 8049H with UV-erasable user-programmable EPROM program memory will soon be available. The 8749 will emulate the 8049H up to 1 MHz clock frequency with minor differences.

The 8049H is fully compatible with the 8049.

These microcomputers are designed to be efficient controllers as well as arithmetic processors. They have extensive bit handling capability as well as facilities for both binary and BCD arithmetic. Efficient use of program memory results from an instruction set consisting mostly of single byte instructions and no instructions over 2 bytes in length.

Table 1. Pin Description

| Symbol                                    | Pin No.        | Function                                                                                                                                                            | Symbol | Pin No. | Function                                                                                                                                            |

|-------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>SS</sub><br>V <sub>DD</sub><br>VCC | 20<br>26<br>40 | Circuit GND potential Low power standby pin Main power supply; +5V during                                                                                           | RD     | 8       | Output strobe activated during a BUS read. Can be used to enable data onto the bus from an external device.                                         |

| PROG                                      | 25             | operation. Output strobe for 8243 I/O                                                                                                                               |        |         | Used as a read strobe to external data memory. (Active low)                                                                                         |

| P10-P17<br>Port 1                         | 27-34          | expander.  8-bit quasi-bidirectional port.                                                                                                                          | RESET  | 4       | Input which is used to initialize the processor. (Active low) (Non TTL V <sub>IH</sub> )                                                            |

| P20-P27<br>Port 2                         | 21-24          | 8-bit quasi-bidirectional port.                                                                                                                                     | WR     | 10      | Output strobe during a bus write. (Active low)                                                                                                      |

|                                           | 35-38          | P20-P23 contain the four high order program counter bits dur-                                                                                                       |        |         | Used as write strobe to external data memory.                                                                                                       |

|                                           |                | ing an external program memory fetch and serve as a 4-bit I/O expander bus for 8243.                                                                                | ALE    | 11      | Address latch enable. This signal occurs once during each cycle and is useful as a clock output.                                                    |

| DB0-DB7<br>BUS                            | 12-19          | True bidirectional port which can be written or read synchronously using the RD, WR strobes. The port can also be                                                   |        |         | The negative edge of ALE strobes address into external data and program memory.                                                                     |

|                                           |                | statically latched.  Contains the 8 low order program counter bits during an external program memory fetch,                                                         | PSEN   | 9       | Program store enable. This output occurs only during a fetch to external program memory.  (Active low)                                              |

|                                           |                | and receives the addressed<br>instruction under the control of<br>PSEN. Also contains the address<br>and data during an external RAM                                | SS     | 5       | Single step input can be used in conjunction with ALE to "single step" the processor through each instruction. (Active low)                         |

|                                           |                | data store instruction, under control of ALE, RD, and WR.                                                                                                           | EA     | 7       | External access input which forces all program memory                                                                                               |

| то                                        | 1              | Input pin testable using the conditional transfer instructions JT0 and JNT0. T0 can be designated as a clock output using ENT0 CLK instruction.                     |        |         | fetches to reference external<br>memory. Useful for emulation<br>and debug, and essential for<br>testing and program verification.<br>(Active high) |

| T1                                        | 39             | Input pin testable using the JT1, and JNT1 instructions. Can be designated the timer/counter                                                                        | XTAL1  | 2       | One side of crystal input for internal oscillator. Also input for external source. (Non TTL V <sub>IH</sub> )                                       |

|                                           |                | input using the STRT CNT instruction.                                                                                                                               | XTAL2  | 3       | Other side of crystal input.                                                                                                                        |

| INT ·                                     | 6              | Interrupt input. Initiates an interrupt if interrupt is enabled. Interrupt is disabled after a reset. Also testable with conditional jump instruction. (Active low) |        |         |                                                                                                                                                     |

|                                           |                |                                                                                                                                                                     |        |         |                                                                                                                                                     |

### 8049H/8039HL

Table 2. Instruction Set

| Accumulator    |                               |       |        |

|----------------|-------------------------------|-------|--------|

| Mnemonic       | Description                   | Bytes | Cycles |

| ADD A, R       | Add register to A             | 1     | 1      |

| ADD A, @R      | Add data memory to A          | 1     | 1      |

| ADD A, # data  | Add immediate to A            | 2     | 2      |

| ADDC A, R      | Add register with carry       | 1     | 1      |

| ADDC A, @R     | Add data memory with carry    | 1     | 1      |

| ADDC A, # data | Add immediate with carry      | 2     | 2      |

| ANL A, R       | And register to A             | 1     | 1      |

| ANL A, @R      | And data memory to A          | 1     | 1      |

| ANL A, # data  | And immediate to A            | 2     | 2      |

| ORL A, R       | Or register to A              | 1     | 1      |

| ORL A @R       | Or data memory to A           | 1     | 1      |

| ORL A, # data  | Or immediate to A             | 2     | 2      |

| XRL A, R       | Exclusive or register to A    | 1     | 1      |

| XRL A, @R      | Exclusive or data memory to A | 1     | 1      |

| XRL, A, # data | Exclusive or immediate to A   | 2     | 2      |

| INC A          | Increment A                   | 1     | 1      |

| DEC A          | Decrement A                   | 1     | 1      |

| CLR A          | Clear A                       | 1     | 1      |

| CPL A          | Complement A                  | 1     | 1      |

| DA A           | Decimal adjust A              | 1     | 1      |

| SWAP A         | Swap nibbles of A             | 1     | 1      |

| RL A           | Rotate A left                 | 1     |        |

| RLC A          | Rotate A left through carry   | 1     | 1      |

| RR A           | Rotate A right                | 1     | 1      |

| RRC A          | Rotate A right through carry  | 1     | 1      |

| Input/Output   |                           |       |        |

|----------------|---------------------------|-------|--------|

| Mnemonic       | Description               | Bytes | Cycles |

| IN A, P        | Input port to A           | 1     | 2      |

| OUTL P. A      | Output A to port          | 1     | 2      |

| ANL P, # data  | And immediate to port     | 2     | 2      |

| ORL P. # data  | Or immediate to port      | 2     | 2      |

| INS A. BUS     | Input BUS to A            | 1     | 2      |

| OUTL BUS, A    | Output A to BUS           | 1     | 2      |

| ANL BUS. # dat | a And immediate to BUS    | 2     | 2      |

| ORL BUS, # dat | a Or immediate to BUS     | 2     | 2      |

| MOVD A.P       | Input expander port to A  | 1     | 2      |

| MOVD P. A      | Output A to expander port | 1     | 2      |

| ANLD P. A      | And A to expander port    | 1     | 2      |

| ORLD P. A      | Or A to expander port     | 1     | 2      |

| Registers |                       |              |

|-----------|-----------------------|--------------|

| Mnemonic  | Description           | Bytes Cycles |

| INC R     | Increment register    | 1 1          |

| INC @R    | Increment data memory | 1 1          |

| DEC R     | Decrement register    | 1 1          |

| Branch       |                             |       |        |

|--------------|-----------------------------|-------|--------|

| Mnemonic     | Description                 | Bytes | Cycles |

| JMP addr     | Jump unconditional          | 2     | 2      |

| JMPP @A      | Jump indirect               | 1     | 2      |

| DJNZ R, addr | Decrement register and skip | 2     | 2      |

| JC addr      | Jump on carry = 1           | 2     | 2      |

| JNC addr     | Jump on carry = 0           | 2     | 2      |

| JZ addr      | Jump on A zero              | 2     | 2      |

| JNZ addr     | Jump on A not zero          | 2     | 2      |

| JTO addr     | Jump on TO = 1              | 2     | 2      |

| JNTO addr    | Jump on TO = 0              | 2     | 2      |

| JT1 addr     | Jump on T1 = 1              | 2     | 2      |

| JNT1 addr    | Jump on T1 = 0              | 2     | 2      |

| JF0 addr     | Jump on F0 = 1              | 2     | 2      |

| JF1 addr     | Jump on F1 ≈ 1              | 2     | 2      |

| JTF addr     | Jump on timer flag          | 2     | 2      |

| JN1 addr     | Jump on INT = 0             | 2     | 2      |

| JBb addr     | Jump on accumulator bit     | 2     | 2      |

| Subroutine |                           |       |        |

|------------|---------------------------|-------|--------|

| Mnemonic   | Description               | Bytes | Cycles |

| CALL addr  | Jump to subroutine        | 2     | 2      |

| RETR       | Return                    | 1     | 2      |

| RETR       | Return and restore status | 1     | 2      |

| Flags    |                   |              |

|----------|-------------------|--------------|

| Mnemonic | Description       | Bytes Cycles |

| CLR C    | Clear carry       | 1 1          |

| CPL C    | Complement carry  | 1 1          |

| CLR F0   | CLear flag 0      | 1 1          |

| CPL F0   | Complement flag 0 | 1 1          |

| CLR F1   | Clear flag 1      | 1 1          |

| CPL F1   | Complement flag 1 | 1 1          |

| Data Moves    | W. 2                              |       |        |

|---------------|-----------------------------------|-------|--------|

| Mnemonic      | Description                       | Bytes | Cycles |

| MOV A, R      | Move register to A                | 1     | 1      |

| MOV A, @R     | Move data memory to A             | 1     | 1      |

| MOV A, # data | Move immediate to A               | 2     | 2      |

| MOV R, A      | Move A to register                | 1     | 1      |

| MOV @R, A     | Move A to data memory             | 1     | 1      |

| MOV R, # data | Move immediate to register        | 2     | 2      |

| MOV @R, #data | Move immediate to data memory     | 2     | 2      |

| MOV A. PSW    | Move PSW to A                     | 1     | 1      |

| MOV PSW, A    | Move A to PSW                     | 1     | 1      |

| XCH A, R      | Exchange A and register           | 1     | 1      |

| XCH A, @R     | Exchange A and data memory        | 1     | 1      |

| XCHD A, @R    | Exchange nibble of A and register | 1     | 1      |

| MOVX A, @R    | Move external data memory to A    | 1     | 2      |

| MOVX @R, A    | Move A to external data memory    | 1     | 2      |

| MOVP A, @A    | Move to A from current page       | 1     | 2      |

| MOVP3 A, @    | Move to A from page 3             | 1     | 2      |

| Mnemonic  | Description                     | Bytes | Cycles |

|-----------|---------------------------------|-------|--------|

| MOV A, T  | Read timer/counter              | 1     | 1      |

| MOV T, A  | Load timer/counter              | 1     | 1      |

| STRT T    | Start timer                     | 1     | 1      |

| STRT CNT  | Start counter                   | 1     | 1      |

| STOP TONT | Stop timer/counter              | 1     | 1      |

| EN TCNT1  | Enable timer/counter interrupt  | 1     | 1      |

| DIS TONT1 | Disable timer/counter interrupt | 1     | 1      |

| Control   |                            |       |        |

|-----------|----------------------------|-------|--------|

| Mnemonic  | Description                | Bytes | Cycles |

| EN 1      | Enable external interrupt  | 1     | 1      |

| DIS 1     | Disable external interrupt | 1     | 1      |

| SEL RB0   | Select register bank 0     | 1     | 1      |

| SEL RB1   | Select register bank 1     | 1     | 1      |

| SEL MB0   | Select memory bank 0       | 1     | 1      |

| SEL MB1   | Select memory bank 1       | 1     | 1      |

| ENT 0 CLK | Enable clock output on T0  | 1     | 1      |

| Mnemonic | Description  | Bytes Cycle | 8 |

|----------|--------------|-------------|---|

| NOP      | No operation | 1 1         |   |

5-54 AFN-01784A-03

#### **ABSOLUTE MAXIMUM RATINGS\***

Ambient Temperature Under Bias ..... 0°C to 70°C Storage Temperature ...... -65°C to + 150°C Voltage On Any Pin With Respect to Ground ..... -0.5V to +7V Power Dissipation ..... 1.5 Watt

\*NOTICE: Stresses above those listed under "Absolute-Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

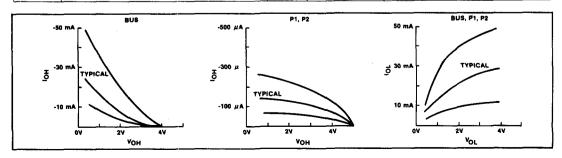

#### D.C. CHARACTERISTICS (TA = 0°C to 70°C, V<sub>CC</sub> = V<sub>DD</sub> = 5V ± 10%, V<sub>SS</sub> = 0V)

| Sumbal           | Parameter                                               |      | Limits |             |      | Test Conditions                                           |  |

|------------------|---------------------------------------------------------|------|--------|-------------|------|-----------------------------------------------------------|--|

| Symbol           | Parameter                                               | Min. | Тур.   | Max.        | Unit |                                                           |  |

| VIL              | Input Low Voltage<br>(All Except RESET, X1, X2)         | 5    |        | .8          | V    |                                                           |  |

| V <sub>IL1</sub> | Input Low Voltage<br>(RESET, X1, X2)                    | 5    |        | .6          | ٧    |                                                           |  |

| V <sub>IH</sub>  | Input High Voltage<br>(All Except XTAL1, XTAL2, RESET)  | 2.0  |        | vcc         | ٧    |                                                           |  |

| V <sub>IH1</sub> | Input High Voltage (X1, X2, RESET)                      | 3.8  |        | Vсс         | ٧    |                                                           |  |

| VOL              | Output Low Voltage (BUS)                                |      |        | .45         | ٧    | I <sub>OL</sub> = 2.0 mA                                  |  |

| V <sub>OL1</sub> | Output Low Voltage<br>(RD, WR, PSEN, ALE)               |      |        | .45         | ٧    | I <sub>OL</sub> = 1.8 mA                                  |  |

| V <sub>OL2</sub> | Output Low Voltage (PROG)                               |      |        | .45         | ٧    | I <sub>OL</sub> = 1.0 mA                                  |  |

| V <sub>OL3</sub> | Output Low Voltage<br>(All Other Outputs)               |      |        | .45         | ٧    | I <sub>OL</sub> = 1.6 mA                                  |  |

| Vон              | Output High Voltage (BUS)                               | 2.4  |        |             | ٧    | I <sub>OH</sub> ≈-400 μA                                  |  |

| V <sub>OH1</sub> | Output High Voltage<br>(RD, WR, PSEN, ALE)              | 2.4  |        |             | ٧    | l <sub>OH</sub> ≈-100 μA                                  |  |

| V <sub>OH2</sub> | Output High Voltage<br>(All Other Outputs)              | 2.4  |        |             | ٧    | I <sub>OH</sub> =-40 μ A                                  |  |

| L1               | Input Leakage Current (T1, INT)                         |      |        | <u>+</u> 10 | μΑ   | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>       |  |

| lLI1             | Input Leakage Current<br>(P10-P17, P20-P27, EA, SS)     |      |        | -500        | μΑ   | V <sub>SS</sub> + .45 ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> |  |

| LO               | Output Leakage Current (BUS, TO) (High Impedance State) |      |        | <u>+</u> 10 | μΑ   | V <sub>SS</sub> + .45 ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> |  |

| I <sub>DD</sub>  | V <sub>DD</sub> Supply Current                          |      | 5      | 10          | mA   |                                                           |  |

| IDD *            | Total Supply Current                                    |      | 50     | 100         | mA   |                                                           |  |

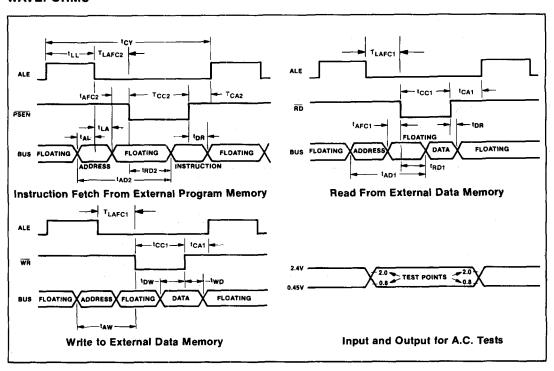

## **A.C. CHARACTERISTICS** $(T_A = 0^{\circ}C \text{ to } 70^{\circ}C, V_{CC} = V_{DD} = 5V \pm 10\%, V_{SS} = OV)$

| Symbol             | Parameter                     | f (t <sub>CY</sub> )<br>(Note 3) | 111  | 11 MHz |      | Conditions |

|--------------------|-------------------------------|----------------------------------|------|--------|------|------------|

|                    |                               |                                  | Min. | Max.   | Unit | (Note 1)   |

| t <sub>LL</sub>    | ALE Pulse Width               | 7/30 t <sub>CY</sub> -170        | 150  |        | ns   |            |

| t <sub>AL</sub>    | Addr Setup to ALE             | 1/5 t <sub>CY</sub> -110         | 160  |        | ns   |            |

| t <sub>LA</sub>    | Addr Hold from ALE            | 1/15 t <sub>CY</sub> -40         | 50   |        | ns   |            |

| t <sub>CC1</sub>   | Control Pulse Width (RD, WR)  | 1/2 t <sub>CY</sub> -200         | 480  |        | ns   |            |

| t <sub>CC2</sub>   | Control Pulse Width (PSEN)    | 2/5 t <sub>CY</sub> -200         | 350  |        | ns   |            |

| t <sub>DW</sub>    | Data Setup before WR          | 13/30 t <sub>CY</sub> -200       | 390  |        | ns   |            |

| t <sub>WD</sub>    | Data Hold after WR            | 1/5 t <sub>CY</sub> -150         | 120  |        | ns   | (Note 2)   |

| t <sub>DR</sub>    | Data Hold (RD, PSEN)          | 1/10 t <sub>CY</sub> -30         | 0    | 110    | ns   |            |

| t <sub>RD1</sub>   | RD to Data in                 | 2/5 t <sub>CY</sub> -200         |      | 350    | ns   |            |

| t <sub>RD2</sub>   | PSEN to Data in               | 3/10 t <sub>CY</sub> -200        |      | 210    | ns   |            |

| t <sub>AW</sub>    | Addr Setup to WR              | 2/5 t <sub>CY</sub> -150         | 300  |        | ns   |            |

| t <sub>AD1</sub>   | Addr Setup to Data (RD)       | 23/30 t <sub>CY</sub> -250       |      | 750    | ns   |            |

| t <sub>AD2</sub>   | Addr Setup to Data (PSEN)     | 3/5 t <sub>CY</sub> -250         |      | 480    | ns   |            |

| t <sub>AFC1</sub>  | Addr Float to RD, WR          | 2/15 t <sub>CY</sub> -40         | 140  |        | ns   |            |

| t <sub>AFC2</sub>  | Addr Float to PSEN            | 1/30 t <sub>CY</sub> -40         | 10   |        | ns   |            |

| t <sub>LAFC1</sub> | ALE to Control, (RD, WR)      | 1/5 t <sub>CY</sub> -75          | 200  |        | ns   |            |

| tLAFC2             | ALE to Control (PSEN)         | 1/10 t <sub>CY</sub> -75         | 60   |        | ns   |            |

| t <sub>CA1</sub>   | Control to ALE (RD, WR, PROG) | 1/15 t <sub>CY</sub> -40         | 50   |        | ns   |            |

| t <sub>CA2</sub>   | Control to ALE (PSEN)         | 4/15 t <sub>CY</sub> -40         | 320  |        | ns   |            |

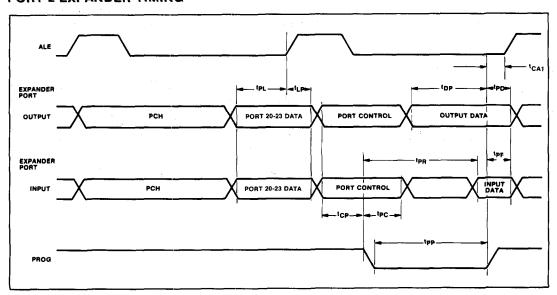

| t <sub>CP</sub>    | Port Control Setup to PROG    | 1/10 t <sub>CY</sub> -40         | 100  |        | ns   |            |

| t <sub>PC</sub>    | Port Control Hold to PROG     | 4/15 t <sub>CY</sub> -200        | 160  |        | ns   |            |

| t <sub>PR</sub>    | PROG to P2 Input Valid        | 17/30 t <sub>CY</sub> -120       |      | 650    | ns   |            |

| t <sub>PF</sub>    | Input Data Hold from PROG     | 1/10 t <sub>CY</sub>             | 0    | 140    | ŋs   |            |

| t <sub>DP</sub>    | Output Data Setup             | 2/5 t <sub>CY</sub> -150         | 400  |        | ns   |            |

| t <sub>PD</sub>    | Output Data Hold              | 1/10 t <sub>CY</sub> -50         | 90   |        | ns   |            |

| t <sub>PP</sub>    | PROG Pulse Width              | 7/10 t <sub>CY</sub> -250        | 700  |        | ns   |            |

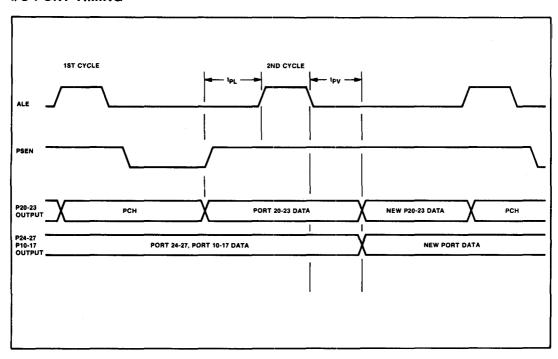

| tPL                | Port 2 I/O Setup to ALE       | 4/15 t <sub>CY</sub> -200        | 160  |        | ns   |            |

| t <sub>LP</sub>    | Port 2 I/O Hold to ALE        | 1/10 t <sub>CY</sub> -100        | 40   |        | ns   |            |

| t <sub>PV</sub>    | Port Output from ALE          | 3/10 t <sub>CY</sub> +100        |      | 510    | ns   |            |

| t <sub>CY</sub>    | Cycle Time                    |                                  | 1.36 |        | μs   |            |

| t <sub>OPRR</sub>  | t0 Rep Rate                   | 3/15 t <sub>CY</sub>             | 270  |        | ns   |            |

#### Notes:

<sup>1.</sup> Control Outputs CL = 80pF BUS Outputs CL = 150pF

<sup>2.</sup> BUS High Impedance Load 20pF

<sup>3.</sup> Calculated values will be equal to or better than published 8049 values.

#### **WAVEFORMS**

#### **PORT 2 EXPANDER TIMING**

#### I/O PORT TIMING

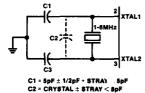

#### **OSCILLATOR MODE**

C2 = CRYSTAL ± STRAY < SpF C3 = 20pF + 1pF ± STRAY < 5pF

CRYSTAL SERIES RESISTANCE SHOULD BE LESS THAN 75  $\Omega$  AT 6MHz; LESS THAN 180  $\Omega$  AT 3.6MHz.

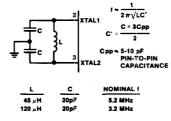

#### LC OSCILLATOR MODE

EACH C SHOULD BE APPROXIMATELY 20pF, INCLUDING STRAY CAPACITANCE.

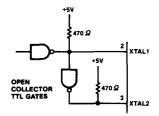

# DRIVING FROM EXTERNAL SOURCE

FOR THE 8048, XTAL1 MUST BE HIGH 35-65% OF THE PERIOD AND XTAL2 MUST BE HIGH 35-65% OF THE PERIOD.

RISE AND FALL TIMES MUST NOT EXCEED 20ns.