# VOICE SYNTHESIZING LSI ADOPTING FORMANT PARAMETERS

The  $\mu$ PD7752 is an LSI for voice synthesis which employs formant data as accumulated parameters. With 5 filters corresponding to the first to fifth formants, vocal characteristics are reproduced to synthesize a voice of quality at a bit rate as low as 2 400 bps. The  $\mu$ PD7752 can be connected easily to any bus system in the microcomputers of the 8080A family. Through serial interfaces, the LSI can also be connected to various other microcomputers. The  $\mu$ PD7752 operates with attractive low power consumption because of its CMOS structure.

#### **FEATURES**

- Voice synthesizing system with formant parameters.

- 5 formants First to fifth

- Bit rate variable between 5 600 and 2 400 bps.

- 32K-bit ROM for voice data storage (voice generating time: approx. 13 seconds at 2 400 bps)

A maximum of 63 messages are selectable.

- External formant parameter ROM (option)

- 9-bit D/A converter a function provided to interface an external D/A converter.

- 3 different voice synthesizing speeds. (SLOW, NORMAL and FAST are selectable.)

- Frame cycle (10 ms or 20 ms) is selectable.

- Bus-compatible with the 8080A, 8085A and 8048.

- Serial interface for mode/Command input.

- Clock oscillator circuit.

- CMOS structure.

- +5 V single power supply.

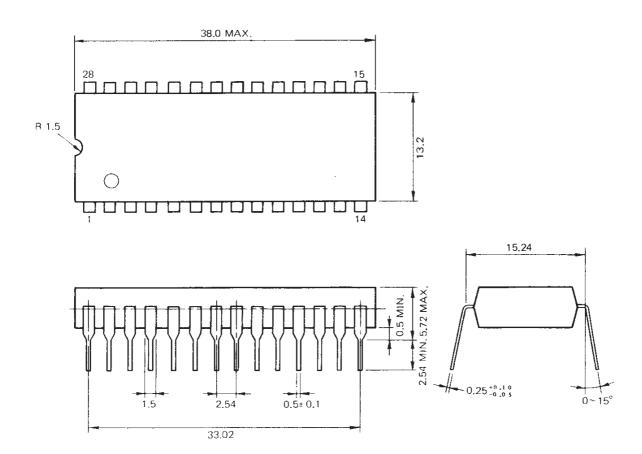

- 28 pin plastic DIP.

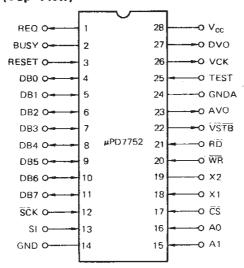

#### CONNECTION DIAGRAM (Top View)

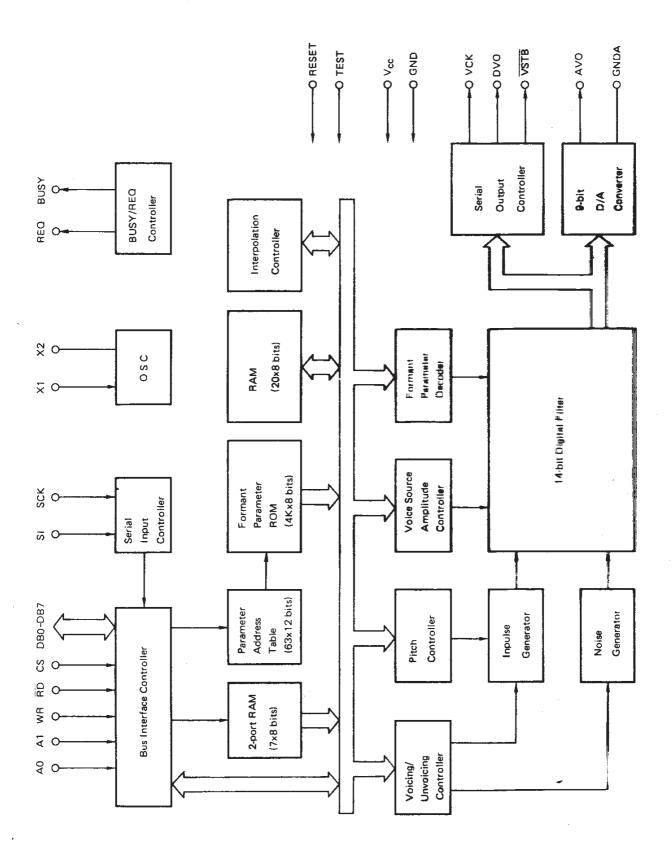

## BLOCK DIAGRAM OF µPD7752

## FUNCTIONAL PIN DESCRIPTION OF µPD7752

(1) DB0 ~ DB7 (Data Bus) - Three-state input/output

These terminals constitute an eight-bit bidirectional data bus which allows the input of mode, command and formant parameter data to the  $\mu$ PD7752, and the output of internal status information from the  $\mu$ PD7752.

(2) CS (Chip Select) - Input

When a low-level signal is applied to this input terminal, data transfer through the data bus is enabled. (This input terminal is independent of the voice output system.)

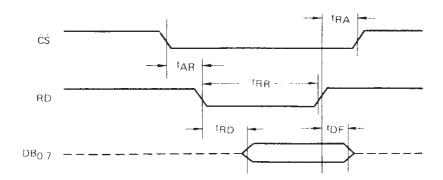

(3) RD (Read) - Input

When a low-level signal is applied to both  $\overline{CS}$  terminal and  $\overline{RD}$  terminal, the status information stored in the status register of the  $\mu PD7752$  is output to the data bus irrespective of the input specification by A0 and A1 terminals.

(4) WR (Write) - Input

When a low-level signal is applied to both  $\overline{CS}$  terminal and  $\overline{WR}$  terminal, the mode, command, or formant parameter data on the data bus is input to the  $\mu PD7752$  as specified by A0 and A1 terminals.

(5) A0 and A1 - Input

These input signals are used in conjunction with  $\overline{WR}$  signal to identify the input data on the bus as a mode, command, or formant parameter. The operations of the  $\mu PD7752$  specified by  $\overline{CS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , A0 and A1 terminals are as follows:

| CS | RD | WR | A0 | A1 | Operation               |

|----|----|----|----|----|-------------------------|

| 1  | ×  | ×  | ×  | Х  | No operation            |

| 0  | 0  | 1  | Х  | ×  | Status read             |

| 0  | 1  | 0  | 0  | 0  | Formant parameter write |

| 0  | 1  | 0  | 0  | 1  | Mode write              |

| 0  | 1  | 0  | 1  | 0  | Prohibited              |

| 0  | 1  | 0  | 1  | 1  | Command write           |

X · Don't care

A0 terminal is also used for selection between mode and command when a mode or command data is to be serially input through SI terminal.

#### (6) SI (Serial Input) - Input

This terminal is used to serially input a mode or command data. A mode or command selection is specified by A0 terminal.

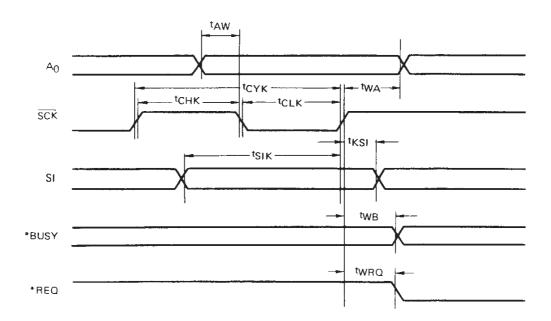

#### (7) SCK (Serial Clock) - Input

This terminal is used to input the transfer clock for the SI (Serial Input) signal.

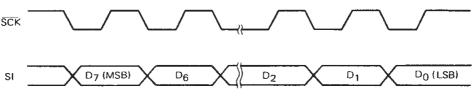

When using the  $\mu$ PD7752 in parallel input mode, fix this terminal at High level. Fig. 1 shows the serial input timing for data transfer to the  $\mu$ PD7752.

Dn (n =  $0 \sim 7$ ): Input Data

Fig. 1 Serial Input Timing

#### (8) BUSY (Busy) - Output

This output terminal is used to indicate whether or not a voice synthesizing operation is being performed by the  $\mu$ PD7752.

This terminal outputs a high-level signal when the  $\mu$ PD7752 accepts a voice generating instruction (to write an internal or external message select command) from an external device.

A low-level signal is output from this terminal under any of the following conditions

- When a voice synthesizing process has been completed.

- When an error occurs during a voice generation using the formant parameters stored in an external ROM.

- When the STOP command is input from an external device during a voice generation.

The voltage level at this terminal remains unchanged even when a new voice generating instruction is applied with the terminal at High level.

#### (9) REQ (Request) - Output

This terminal outputs a high-level signal when the  $\mu$ PD7752 requests a formant parameter in the voice generation using an external formant parameter ROM. A low-level signal is output from this terminal when a formant parameter from the external ROM has been written according to the REQ signal. When the  $\mu$ PD7752 requires an additional formant parameter, the terminal outputs a high-level signal again.

The REQ terminal outputs a low-level signal, following the low-level signal output from the BUSY terminal (namely, when an error occurs in the transfer of a formant parameter or when the stop command is accepted by the  $\mu$ PD7752). A low-level signal, however, is output when a voice generation is performed using the formant parameters stored in the internal ROM.

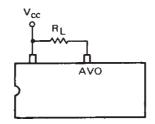

#### (10) AVO (Analog Voice Output) - Output

This terminal is used to output a voice signal converted into an analog level by the 9-bit D/A converter. Because of the current output type, this terminal requires an external load resistor.

#### (11) GNDA (Ground for Analog Signal)

Ground potential for the AVO (Analog Voice Output).

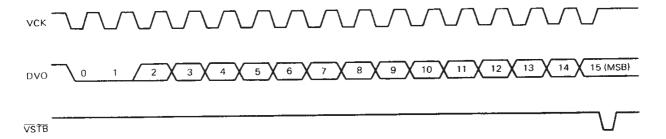

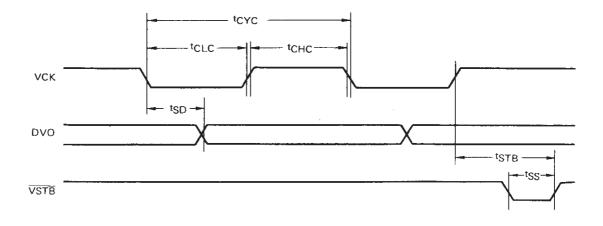

#### (12) DVO (Digital Voice Output) - Output

This terminal is used to serially output formant parameter as a 16-bit digital data starting from its LSB.

Of the 16 bit, 14 bits from MSB are effective as the formant parameter and the remaining 2 bits (from LSB) are dummy outputs (0).

#### (13) VCK (Voice Clock) - Output

This terminal is used to output a clock for synchronizing the DVO (Digital Voice Output) signal. For a DVO output, this terminal outputs 16 clock pulses.

## (14) VSTB (Voice Output Strobe)

This terminal is used to output a strobe indicating that the serial data have been output from the DVO in the required 16 bits. The serial data output timing is shown in Fig. 2.

Fig. 2 Serial Data Output Timing

## (15) X1, X2

These terminals are used to connect a 3.6 MHz crystal (a 3.579545 MHz crystal may be employed) or ceramic oscillator for clock oscillation. The X1 line is used to input an externally supplied clock.

- (16) RESET (Reset) Input

- This terminal is used to input an active high signal for system reset.

- (17) TEST (Test) Input

This input terminal is used for the LSI testing and is normally tied to the GND.

- (18) V<sub>cc</sub>

- +5 V power supply for the LSI.

- (19) GND

Ground potential for the LSI.

## BASIC OPERATION OF $\mu$ PD7752

As flowcharted in Fig. 3, the basic operations of the  $\mu$ PD7752 are broadly divided into the following three categories:

Fig. 3 Operating Procedure

#### (1) Mode selection

This operation is to select a voice synthesizing speed and an analytic frame cycle.

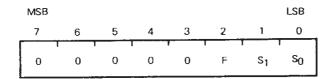

The format of the mode data for the  $\mu PD7752$  is shown in Fig. 4.

With this operation, one of the three voice synthesizing speeds (Normal speed and two speeds at  $\pm 20$  % of Normal), and either of the two frame cycles are selectable.

F: Analytic Frame Bits

F = 0 10 ms/frame

F = 1 20 ms/frame

S1, S0: Synthesizing Speed Bits

S1 = 0, S0 = 0 : Normal Speed

S1 = 0, S0 = 1: Slow Speed

S1 = 1, S0 = 0 : Fast Speed

S1 = 1, S0 = 1: Disabled

Fig. 4 Mode Data

- (a) Upon input of the RESET signal, the  $\mu$ PD7752 is set in the mode for Normal Speed (S1 = 0, S0 = 0), and 10 ms/frame (F = 0).

- (b) The  $\mu$ PD7752 operates in the previously set mode until a new mode data is written into the  $\mu$ PD7752.

- (c) When a new mode data is set after a command input, the newly set mode becomes effective upon input of the next command.

#### Mode data input procedures

A mode data can be written into the  $\mu$ PD7752 parallelly through DB0~DB7 terminals or serially through SI terminal.

## 1) Parallel input method

The mode can be specified by setting an 8-bit mode data on DB0~DB7 terminals, turning the voltage levels at A0 and A1 terminals to low and high, respectively and by applying a signal to WR terminal. For this setting, however, SCK terminal must be fixed at High level.

#### 2) Serial input method

Serial data can be input to the  $\mu$ PD7752 by applying serial clock pulse to SI and SCK terminals with the voltage levels at A0, A1 and CS terminals set at low, high and low, respectively. (8-bit serial data is input one by one starting from its MSB.) For this setting, however, WR and RD terminals must be fixed at high level.

For mode and command data input, either of the serial and parallel input methods descrived above must be used throughout. If the serial input method is used for a mode data input, the same method should be used for a command data input as well.

#### (2) Command Input

In this operation, the control data (i.e., command) for a message to be voiced is entered.

(a) Type of command

The following three types of control data are used.

1) Internal Message Select Command

This command instructs the  $\mu$ PD7752 to execute a voice generation using the messages stored in the internal ROM.

2) Stop Command

This command instructs the  $\mu$ PD7752 to stop the voice message being generated.

3) External Message Select Command

This command instructs the  $\mu$ PD7752 to execute a voice generation using the formant parameters stored in the external ROM.

(b) Command data input procedures

A command data can be input to the  $\mu$ PD7752 parallelly through DB0 $\sim$ DB7 terminals from or serially through SI terminal.

1) Parallel input method

Observe the same procedure as in the mode selection, except that both A0 and A1 terminals must be set at high level.

2) Serial input method

Observe the same procedure as in the mode selection except that A0 terminals must be set at high level

- (c) Description of each command

- 1) Internal Message Select Command

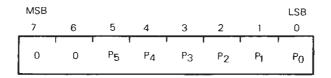

Fig. 5 shows the data format of this command.

$P_5 \sim P_0$ : Message select bits

Fig. 5 Internal Message Select Command

| _P5 | P4 | P3 | _P2 | P1 | PO  | _           |

|-----|----|----|-----|----|-----|-------------|

| 0   | 0  | 0  | 0   | 0  | 0 ) | -           |

| :   | :  | :  | :   | :  | : [ | 63 messages |

| :   | 1  | :  | :   | :  | : [ | OD Messages |

| 1   | 1  | 1  | 1   | 1  | 0   |             |

| 1   | 1  | 1  | 1   | 1  | 1 } | Prohibited  |

Upon writing an internal message select command into the  $\mu$ PD7752 a message specified by the message select bits is automatically voiced. If another internal message select command is written into the  $\mu$ PD7752 during a voice generation, the  $\mu$ PD7752 immediately voices an internally specified message according to the newly given command.

#### 2) Stop Command

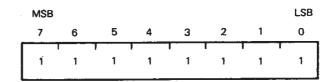

When this command is input, the voice generation being executed is discontinued immediately. Fig. 6 shows the data format of this command.

Fig. 6 Stop Command

Upon writing the stop command into the  $\mu$ PD7752, the contents of the status register (refer to paragraph (3) below) are all set to zeros.

However, the set mode remains unchanged.

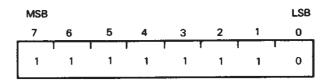

#### 3) External Message Select Command

Fig. 7 External Message Select Command

This command instructs the  $\mu$ PD7752 to generate a voice using the formant parameters stored in the external ROM. After this command is written into the  $\mu$ PD7752, formant parameters stored in the external ROM must be input by the processor to the  $\mu$ PD7752 in units of 1 byte through D80~D87 terminals according to the REQ signal output from the  $\mu$ PD7752.

#### <Data transfer>

#### (a) Formant parameter

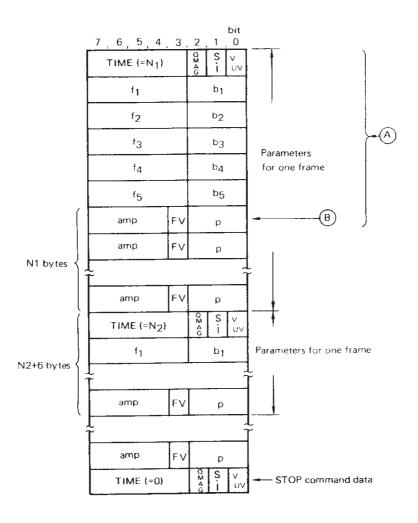

The formant parameters used for voice generation according to the Internal or External Message Select Command are stored in the internal ROM of the  $\mu$ PD7752 or external ROM in the data format as shown in Fig. 8.

Fig. 8 Formant Parameter

TIME: Time data It indicates the number of frames by which data fn and bn  $(n=1\sim5)$  are to be applied repeatedly.

QMAG: Quantized magnification data

S.I.: Selective interpolation data V/UV: Voicing/Unvoicing data

fn: Formant frequency

bn: Formant band width (resonance strength)

amp: Voice source amplitudeFV: Fricative Voice data

p: Pitch

For detailed description of each parameter, refer to the  $\mu\,\text{PD7752}$  Users Manual.

#### (b) Method to transfer formant parameters

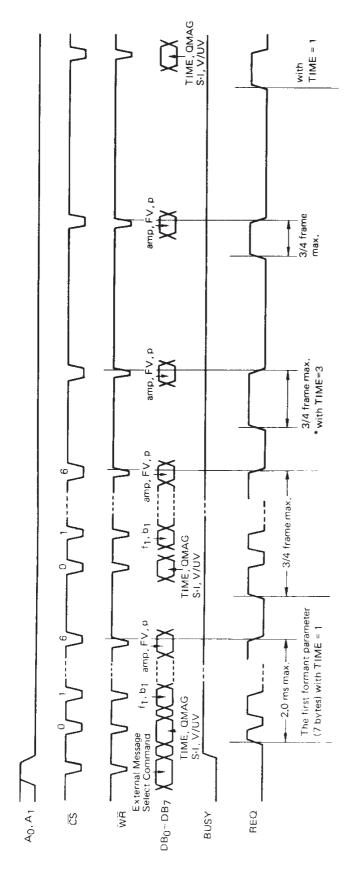

In executing the transfer of formant parameters according to the REQ signal after an External Message Select Command has been written into the  $\mu$ PD7752, pay attention to the following matters.

- 1) Transfer formant parameters according to the REQ signal. The transfer of a parameter can only be accomplished when the REQ signal is at high level.

- In Figs. 9 and 10, the timing of the REQ signal is shown.

- 2) Transfer an 8-bit formant parameter parallelly through DB0~DB7 terminals. (Serial transfer cannot be effected.)

- To transfer formant parameters parallelly, be sure to set the voltage level at A0, A1, and  $\overline{\text{CS}}$  terminals to low and apply WR signal.

- 3) Formant parameters (the first 7 bytes) immediately after the output of an External Message Select Command must be transferred within 2.0 ms (within 2.5 ms at Normal Speed, and 3.0 ms at Slow Speed) after the output of the REQ signal.

- 4) For transfer of subsequent formant parameters per frame (see Table 1), be sure to transfer 7 bytes (shown by (A) in Fig. 8 when the REQ signal is output 7 times) or 1 byte (shown by (B) in Fig. 8 when the REQ signal is output only one time) of formant parameter sequentially within 3/4 frame.

\* At the normal vowel part in natural voice, changes in the formant data (frequency: fn, band width: bn) are relatively moderate. Therefore, the μPD7752 employs TIME data in order to repeatedly use the same voice synthesizing data at the part where changes in voice characteristics are not significant. In other words, TIME is the data which indicates the number of times in and brare repeatedly used in the voice synthesizing data (i.e., number of frames). With TIME - 3, the 7 bytes shown by 🕲 in Fig. 8 are used in the first frame, and amp (amplitude), FV (fricative voice) and p (pitch) only are changed in the next frames.

Fig. 9 REQ Timing (At Start of Voice Generation)

Table 1 Formant Parameter Transfer Time

| Analytic frame | 10  | 20 |

|----------------|-----|----|

| SLOW           | 9.0 | 18 |

| NORMAL         | 7.5 | 15 |

| FAST           | 6.0 | 12 |

Unit: ms

If the transfer of formant parameters is not effected in accordance with the above procedure, the  $\mu$ PD7752 processes it as an error.

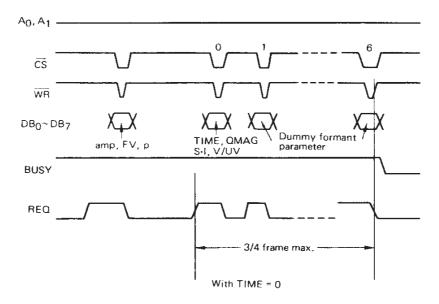

#### (c) Method to terminate formant parameter transfer

The  $\mu$ PD7752 reads and decodes the TIME = 0 data written into the 2-port RAM from an external device, and then terminates the voice generating operation. The  $\mu$ PD7752 reads the TIME data only after the 2-port RAM has been filled with a formant parameter of 6 bytes written subsequent to the TIME data write into the 2-port RAM.

Therefore, to terminates the transfer of formant parameter, it is necessary to write 6 dummy formant parameters in sequence after the TIME = 0 data has been written into the 2-port RAM. If the dummy parameters are not written within 3/4 frame after the TIME data write, the voice generating processing is discontinued after the ERR flag in the status register has become "1".

Fig. 10 REQ Timing (End of Voice Generation)

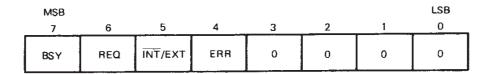

#### (3) Status Register

The status register which indicates the internal status of the  $\mu PD7752$  is shown in Fig. 11.

The contents of this register can be read externally at any time through DBO~DB7 terminals. After the RESET signal input, the contents of the status register are all reset to zeros.

Fig. 11 Status Register

(a) BSY: This bit indicates whether or not the µPD7752 is under voice synthesizing.

Voice synthesizing is in process:

Voice synthesizing is stopped: O

(b) REQ: This bit indicates that the  $\mu$ PD7752 is requesting to input a formant parameter after an External Message Select Command has been written.

Input of a formant parameter is requested:

Input of a formant parameter is disabled:

If an Internal Message Select Command is written, this flag bit becomes 0.

(c) INT/EXT: This bit indicates whether a message has been selected from the internal ROM or external ROM.

A message stored in the internal ROM is selected: 0

A message stored in the external ROM is selected: 1

(d) ERR: This bit indicates whether or not the transfer of a formant parameter from the external ROM to the µPD7752 has been completed properly.

Transferred with an error:

Transferred without error:

- 1) The ERR flag bit becomes 1 in the following cases.

- O When a formant parameter has not been written into the μPD7752 within a specified period of time with the REQ signal being output.

- $\circ$  When a formant parameter has been written into the  $\mu PD7752$  without the REQ signal being output.

- 2) The ERR flag bit becomes 0 in the following cases.

- When the RESET signal is input to the  $\mu$ PD7752.

- When a new command is written into the  $\mu$ PD7752.

## **ABSOLUTE MAXIMUM RATINGS\***

Operating Temperature . . . . . . 0 °C to +70 °C Storage Temperature . . . . . -65 °C to +150 °C Voltage on Any Pin . . . . .  $V_{CC}$ -0.3 V to  $V_{CC}$ +0.3 V Supply Voltage . . . . .  $V_{SS}$ -0.3 to +10 V

COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

\*  $T_a = 25$  °C

#### DC CHARACTERISTICS

$(T_a = 0 \text{ to } +70 \text{ °C}, V_{CC} = +5 \text{ V } \pm 10 \text{ %, } V_{SS} = 0 \text{ V})$

| CHARACTERISTIC                                             | SYMBOL           | MIN.                 | TYP. | MAX.            | UNIT | TEST CONDITION                                                |

|------------------------------------------------------------|------------------|----------------------|------|-----------------|------|---------------------------------------------------------------|

| Input Low Voltage                                          | VIL              | -0.3                 |      | 0.8             | V    |                                                               |

| Input High Voltage (All Except XTAL1, XTAL2,) (RESET, TEST | VIH              | 2.2                  |      | V <sub>cc</sub> | ٧    |                                                               |

| Input High Voltage (XTAL1, XTAL2, RESET, TEST              | V <sub>IH1</sub> | V <sub>cc</sub> ~1   |      | V <sub>cc</sub> | ٧    |                                                               |

| Output Low Voltage                                         | VOL              |                      |      | 0.45            | V    | IOL=2.0 mA                                                    |

| Output High Voltage                                        | Voн              | 2.4                  |      |                 | ٧    | ΙΟΗ=-400 μΑ                                                   |

| Output High Voltage                                        | VOH1             | V <sub>cc</sub> -0.5 |      |                 | V    | I <sub>OH</sub> =–0.2 μA                                      |

| Input Leakage Current                                      | IIL              |                      |      | ±10             | μΑ   | V <sub>ss</sub> $\leq$ V <sub>IN</sub> $\leq$ V <sub>cc</sub> |

| Output Leakage Current<br>(Bus-High Impedance State)       | lOL              |                      |      | ±10             | μΑ   | $V_{ss} \leq V_O \leq V_{CC}$                                 |

| Total Supply Current                                       | lcc              |                      | 5    | 10              | mA   | t <sub>CY</sub> =275 ns                                       |

# D/A CONVERTER CHARACTERISTICS

(T<sub>a</sub>=0 $\sim$ +70 °C, V<sub>CC</sub>=+5 V ± 10 %, V<sub>SS</sub>=0 V)

| CHARACTERISTIC      | SYMBOL | MIN. | MAX. | UNIT | TEST CONDITION        |

|---------------------|--------|------|------|------|-----------------------|

| MAX. Output Current | IDA    | 0.8  | 4    | mA   | R <sub>L</sub> = 1 kΩ |

| MAX. Output Voltage | VDA    | 0.8  | 4    | ٧    | R <sub>L</sub> = 1 kΩ |

| Sampling Frequency  | fS     | 9.5  | 10.5 | kHz  |                       |

## D/A CONVERTER TEST CIRCUIT

# AC CHARACTERISTICS (Ta=0~+70 °C, $V_{CC}$ =+5 V ± 10 %, $V_{SS}$ =0 V)

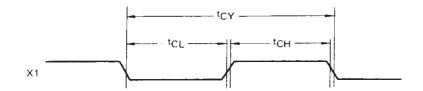

## **CLOCK TIMING**

| CHARACTERISTIC                        | SYMBOL          | MIN. | MAX. | UNIT | TEST CONDITION |

|---------------------------------------|-----------------|------|------|------|----------------|

| X <sub>1</sub> Input Cycle Time       | tCY             | 275  |      | ns   |                |

| X <sub>1</sub> Input Low Level Width  | tCL             | 120  |      | ns   |                |

| X <sub>1</sub> Input High Level Width | <sup>†</sup> CH | 120  |      | ns   |                |

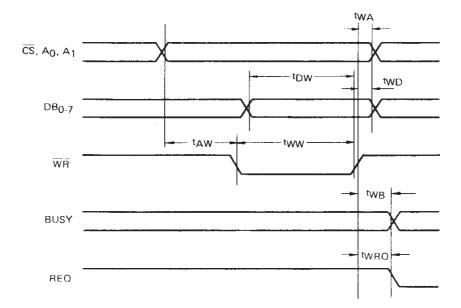

## **READ/WRITE OPERATION**

| CHARACTERISTIC     | SYMBOL | MIN. | MAX. | UNIT | TEST CONDITION                                  |

|--------------------|--------|------|------|------|-------------------------------------------------|

| Address Setup Time | tAW    | 0    |      | ns   |                                                 |

| Address Hold Time  | twA    | 0    |      | ns   |                                                 |

| Data Setup Time    | tDW    | 150  |      | ns   |                                                 |

| Data Hold Time     | tWD    | 0    |      | ns   |                                                 |

| WR Pulse Width     | tww    | 250  |      | ns   |                                                 |

| BUSY Delay         | twB    |      | 600  | ns   | C <sub>L</sub> =150 pF, t <sub>C</sub> Y=280 ns |

| REQ Delay          | tWRQ.  |      | 600  | ns   | CL=150 pF, tCY=280 ns                           |

| Address Setup Time | tAR    | 0    |      | ns   |                                                 |

| Address Hold Time  | tRA    | 0    |      | ns   |                                                 |

| RD Pulse Width     | tRR    | 250  |      | ns   | -                                               |

| Data Delay         | tRD    |      | 170  | ns   | CL=150 pF, tCY=280 ns                           |

| Data Floating      | tDF    |      | 120  | ns   | C <sub>L</sub> =150 pF, t <sub>C</sub> Y=280 ns |

## **SERIAL OPERATION**

| CHARACTERISTIC       | SYMBOL           | MIN. | MAX. | UNIT | TEST CONDITION                                  |

|----------------------|------------------|------|------|------|-------------------------------------------------|

| SCK Cycle Time       | tCYK             | 800  |      | ns   |                                                 |

| SCK Low Level Width  | tCLK             | 350  |      | ns   |                                                 |

| SCK High Level Width | tCHK             | 350  |      | ns   |                                                 |

| SI Setup Time        | <sup>t</sup> SIK | 140  |      | ns   |                                                 |

| SI Hold Time         | tKSI             | 260  |      | ns   |                                                 |

| VCK Cycle Time       | tCYC             | 1500 |      | ns   | CL=150 pF, tCY=280 ns                           |

| VCK Low Level Width  | tCLC             | 500  |      | ns   | C <sub>L</sub> =150 pF, t <sub>C</sub> Y=280 ns |

| VCK High Level Width | tCHC             | 1000 |      | ns   | CL=150 pF, tCY=280 ns                           |

| DVO Delay            | tsD              |      | 180  | ns   | CL=150 pF, tCY=280 ns                           |

| VSTB Delay           | tSTB             |      | 900  | ns   | CL=150 pF, tCY=280 ns                           |

| VSTB Pulse Width     | tSS              | 500  |      | ns   | CL=150 pF, tCY=280 ns                           |

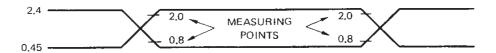

## AC Signal waveform

Output Timing is measured with  $\rm V_{OH}\mbox{=}2.0~V$  and  $\rm V_{OL}\mbox{=}0.8~V.$

# CAPACITANCE (Ta=25 °C, Vcc=GND=0 V)

| CHARACTERISTIC     | SYMBOL           | MIN. | MAX. | UNIT | TEST CONDITION           |

|--------------------|------------------|------|------|------|--------------------------|

| Input Capacitance  | Cl               |      | 10   | pΕ   | f <sub>c</sub> = 1 MHz   |

| Output Capacitance | CO               |      | 20   | ρF   | Unmeasured Pins returned |

| I/O Capacitance    | C <sub>I/O</sub> |      | 20   | рF   | to GND.                  |

## **CLOCK TIMING**

## WRITE OPERATION

## **READ OPERATION**

## **SERIAL OPERATION**

\* BUSY and REQ signal is changed after LSB of COMMAND is supplied.

## PACKAGE DIMENSIONS (Unit: mm)

#### **NEC OFFICES**

NEC Electronics (Europe) GmbH, Oberrather Str. 4, 4000 Düsseldorf 30, W.-Germany, Tel. (0211) 650301, Telex 858996-0

NEC Electronics (Germany) GmbH, Kanzlerstr. 6, 4000 Düsseldorf 30, Tel. (0211) 650302, Telex 858996-0

- Hindenburgstr. 28/29, 3000 Hannover 1, Tel. (0511) 881013-16, Telex 9230109

- Arabellastr. 17, 8000 München 81, Tel. (089) 4160020, Telex 522971

- Heilbronner Str. 314, 7000 Stuttgart 30, Tel. (0711) 890910, Telex 7252220

- NEC Electronics (BNL) 33 Alard du Hamelstraat, 5622 CC Eindhoven, Tel. (040) 445845, Telex 51923

- NEC Electronics (Scandinavia) Box 4039, S-18304 Täby, Tel. (08) 7567245, Telex 13839

NEC Electronics (France) S.A., Tour Chenonceaux, 204, Rond Point du Pont de Sèvres, F-92516 Boulogne Billancourt, Tel. (01) 6 09 90 04, Telex 203 544 NEC Electronics Italiana S.R.L., Via Cardano 3, I-20124 Milano, Tel. (02) 67 09 108, Telex 315 355

NEC Electronics (UK) Ltd., Block 3 Carfin Industrial, Motherwell M L1 4UL, Schottland, Tel. (0698) 732221, Telex 777 565