# VIDEO AND SYSTEM CONTROLLER

# **GENERAL DESCRIPTION**

The SCC66470B is a CMOS Video and System Controller (VSC). Integrating a high resolution bit-mapped colour display and a 680XX family system controller, the SCC66470B considerably reduces system cost.

The SCC66470B can directly drive up to 2 M bytes of memory and provides chip-select signals for both system ROM and peripherals. The on-chip DRAM controller supports up to 1 M bit (256 K x 4) DRAMs and controls access to the combined system/video DRAM. The CPU can access all memory locations even during active video display lines, thus improving system performance while reducing system cost.

## **FEATURES**

INTEGRA

- Full bit-map organization

- Direct interface to 680XX compatible CPUs

- Screen resolution: up to 768 x 560 pixels

- 4 or 8 bits per pixel

- Shift register for up to 15 MHz pixel rate

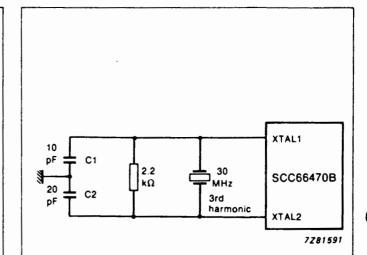

- On-chip oscillator circuitry

- Synchro generator for 50 and 60 Hz scan

- Double frequency scan

- Synchronization with external video

- 1.5 M byte DRAM direct drive capability supporting up to 1 M bit (256 K x 4) DRAMs

- 0.5 M byte ROM control

- 1 K byte I/O control

- Reset sequencer and watchdog timer

- Fast 16-bit pixel test-and-modify logic (PIXAC)

- CMOS technology

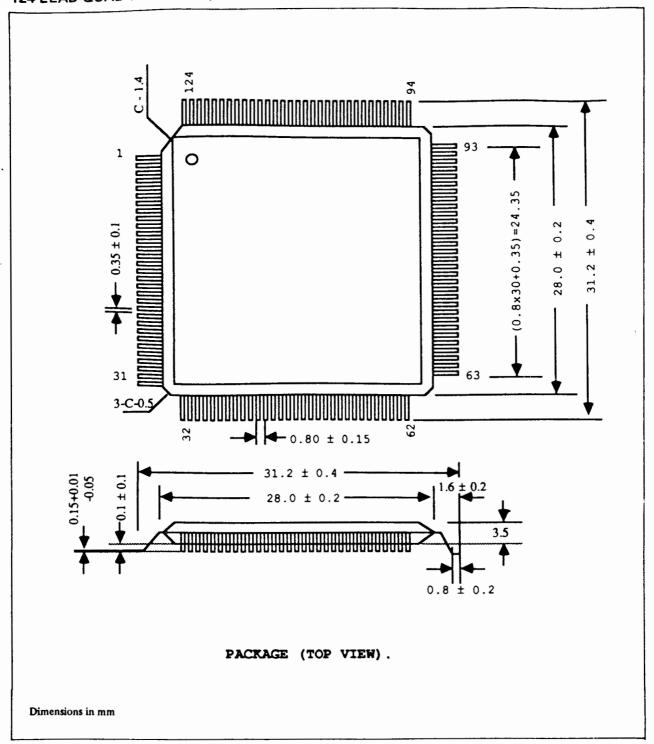

- 124-lead quad flat-pack plastic package

# **APPLICATIONS**

- Home computers

- Personal computers

- Home entertainment

- Intelligent colour terminals

- Graphics, text and I/O systems

The display resolution is programmable and between 16 and 256 colours can be selected per pixel. Studio quality pictures can be obtained by using an additional VSC which increases the number of colours to 2<sup>16</sup>. The display timing is compatible with European, American and Japaneese standards for TV and TELETEXT applications.

# PACKAGE OUTLINES

SCC66470B: 124-lead quad flat-pack; plastic

High-speed pixel manipulation logic (PIXAC) is provided on-chip to accelerate image manipulation (compared to software only pixel manipulation) and a coprocessor interface is provided to permit very fast manipulation of memory. The pixels are organized as PACKED PIXELS and each pixel occupies either a nibble or a byte. This allows fast test-and-modify pixel operations and pixel blitting which is much more powerful than bit blitting.

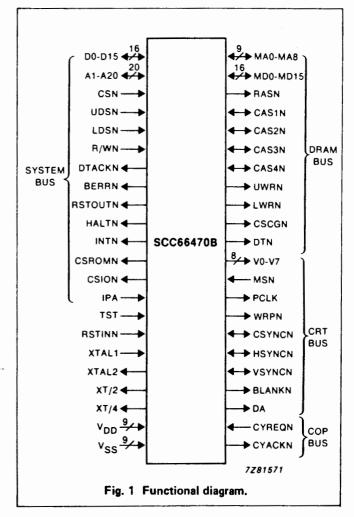

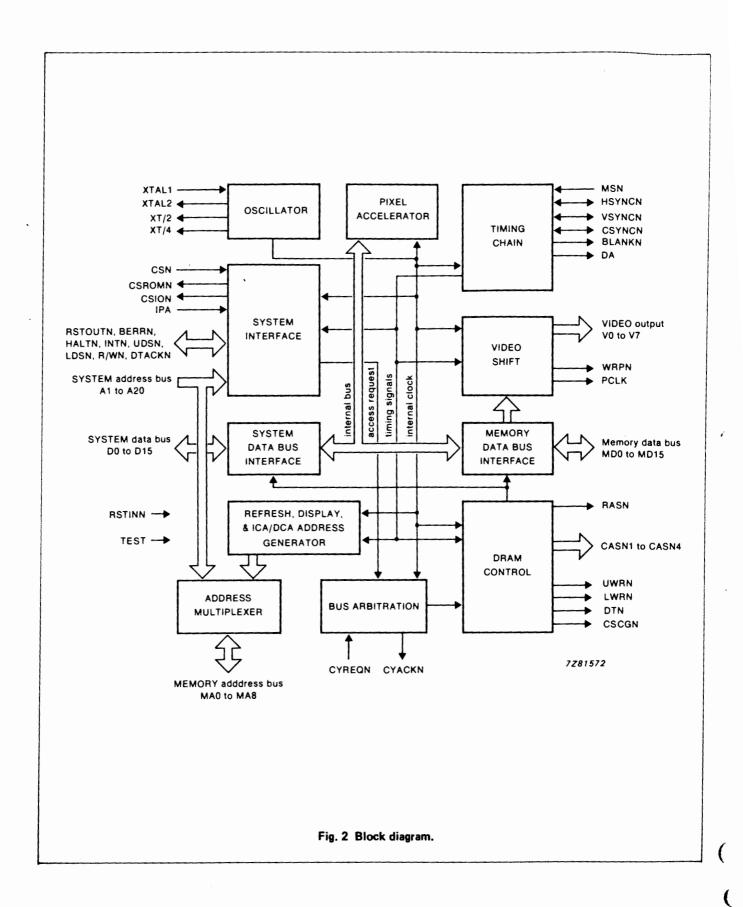

Fig. 1 shows the functional diagram and Fig. 2 shows the block diagram of the SCC66470B. The 680XX system bus is connected via 16 bidirectional data lines, 20 address lines and several control lines. Dynamic RAMS are accessed via 8 or 9 address lines (MA bus), 16 bidirectional data lines (MD bus) and control lines. The video output consists of 8 video data lines and 2 control lines. The pixel accelerator may be accessed via the system bus (by the CPU for example). It may also be accessed via the memory bus (by the coprocessor interface for example).

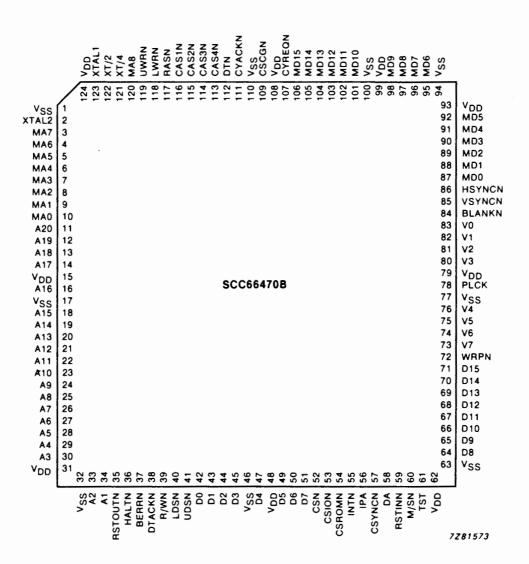

Fig. 3 Pinning diagram.

# SIGNAL DESCRIPTION

| mnemonic | type | pin no.                       | function                                                                                                                                                                                          |

|----------|------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      |                               | System bus                                                                                                                                                                                        |

| A1-A20   | 1    | 11-14, 16,<br>18-30, 33, 34   | System address bus. A1 to A20 provide the system address during system bus accesses. A1—A20 must be stable when LDSN and/or UDSN go LOW.                                                          |

| D0-D15   | 1/0  | 42-45, 47,<br>49-51,<br>64-71 | Bidirectional 3-state data bus which is used to transfer data between the system bus and the VSC. The VSC drives the data bus during read cycles. D0–D15 must be stable when UDSN or LDSN go LOW. |

| UDSN     | 1    | 41                            | Active LOW upper data strobe. When UDSN is LOW, data on D8-D15 is being addressed.                                                                                                                |

| LDSN     | 1    | 40                            | Active LOW lower data strobe. When LDSN is LOW, data on D0-D7 is being addressed.                                                                                                                 |

| R/WN     | ı    | 39                            | Read/write. R/WN determines the data transfer direction on the system bus. When R/WN is LOW, data is being written into VSC controlled recources.                                                 |

| CSN      | ı    | 52                            | Active LOW VSC chip select. CSN validates the address decode for system access.                                                                                                                   |

| DTACKN   | 0    | 38                            | Active LOW, 3-state data transfer acknowledge signal. DTACKN is asserted by the VSC when the system bus cycle can be continued.                                                                   |

| RSTOUTN  | 0    | 35                            | Active LOW, 3-state RESET output. RSTOUTN is asserted by the VSC reset sequencer during the reset procedure.                                                                                      |

| HALTN    | 0    | 36                            | Active LOW, 3-state HALTN output. HALTN is asserted by the VSC reset sequencer during the reset procedure.                                                                                        |

| BERRN    | 0    | 37                            | Active LOW Bus Error output (3-state if programmed). BERRN is asserted by the VSC if UDSN or LDSN are still asserted at the end of the time-out period.                                           |

| CSROMN   | 0    | 54                            | Active LOW ROM chip select. The VSC asserts CSROMN during a system bus access in the ROM address area when UDSN and/or LDSN are asserted.                                                         |

| CSION    | 0    | 53                            | Active LOW I/O chip select. The VSC asserts CSION during a system bus access in the I/O address area when UDSN and/or LDSN are asserted.                                                          |

| INTN     | 0    | 55                            | Active LOW, 3-state interrupt request output. INTN is used to generate interrupt requests to the CPU.                                                                                             |

| IPA      |      | 56                            | Active HIGH, 3-state implicit pixel accelerator addressing input. The CPU uses IPA to implicitly address the VSC pixel accelerator to increase pixel manipulation speed.                          |

**PHILIPS**

|   | _    |

|---|------|

|   | DAT/ |

|   | È    |

| ţ | ڒ    |

|   | ÆLOF |

|   | DEVE |

|   | Ω    |

|   |      |

| mnemonic                         | type | pin no.                  | function                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------|------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  |      |                          | Dynamic RAM interface                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MA0-MA8                          | 1/0  | 3–10, 120                | Memory address lines. These 3-state, multiplexed ROW/COLUMN address line outputs are used for DRAM control. Only MA0—MA7 are significant when 64 K DRAMS are used. MA0—MA8 are the least significant address input bits (A1 to A9) from a coprocessor when the CYACKN output is asserted.                                                                                                                                                 |

| MD0-MD15                         | I/O  | 87-92, 95-98,<br>101-106 | 3-state bidirectional memory data bus. MD0-MD15 also function as address and control inputs during coprocessor cycles.                                                                                                                                                                                                                                                                                                                    |

| RASN                             | 0    | 117                      | Active LOW row address strobe. On the falling edge of RASN, the DRAM row address becomes valid. RASN is also used for coprocessor handshaking.                                                                                                                                                                                                                                                                                            |

| CAS1N<br>CAS2N<br>CAS3N<br>CAS4N | 1/0  | 113116                   | Active LOW column address strobes for memory banks 1 to 4. On the falling edge of CASnN, the column address of memory bank n becomes valid. During the RESET period, CAS1N to CAS4N are active HIGH and validate the memory bank inputs CAS4N is only used with 64 K devices.                                                                                                                                                             |

| CSCGN                            | 0    | 109                      | Active LOW character ROM chip select. CSCGN is only used with the coprocessor interface.                                                                                                                                                                                                                                                                                                                                                  |

| UWRN                             | 0    | 119                      | Active LOW upper write signal for DRAM. It is asserted when the most significant DRAM byte is being written.                                                                                                                                                                                                                                                                                                                              |

| LWRN                             | 0    | 118                      | Active LOW lower write signal for DRAM. LWRN is asserted when the least significant DRAM byte is being written.                                                                                                                                                                                                                                                                                                                           |

| DTN                              | 0    | 112                      | Active LOW data transfer output. DTN is used in dual port video RAM mode.                                                                                                                                                                                                                                                                                                                                                                 |

|                                  |      |                          | CRT controller interface                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V0V7                             | 0    | 73-76, 80-83             | 3-state video outputs. V0-V7 are used to output pixels and control words.                                                                                                                                                                                                                                                                                                                                                                 |

| PCLK                             | 0    | 78                       | 3-state pixel clock. On the rising edge of PCLK, the video output lines (V0-V7) are valid.                                                                                                                                                                                                                                                                                                                                                |

| WRPN                             | 0    | 72                       | Active LOW write palette output. When WRPN is active, data available on V0–V7 is control information. WRPN is used with an external palette or a back-end chip.                                                                                                                                                                                                                                                                           |

| VSYNCN                           | 1/0  | 85                       | Active LOW, 3-state vertical synchronization line. In the Master mode, VSYNCN is used as a vertical synchronization output signal. In the Slave TV and Slave Dual modes, VSYNCN becomes a vertical synchronization input.                                                                                                                                                                                                                 |

| HSYNCN                           | I/O  | 86                       | Active LOW, 3-state horizontal synchronization line. In the Master and Slave TV modes, HSYNCN is used as a horizontal synchronization output signal. In the Slave Dual mode, HSYNC becomes a horizontal synchronization input.                                                                                                                                                                                                            |

| CSYNCN                           | 1/0  | 57                       | Active LOW, 3-state composite synchronization line. In the Master mode, CSYNCN generates a composite synchronization output signal. In the Slave TV mode, CSYNCN generates a symmetrical signal which generates a horizontal frequency. In the Slave Dual mode, CSYNCN generates the phase error between the master VSC and the slave VSC. When the display is disabled, the CSYNCN input is used to initialize the synchronization mode. |

| mnemonic | type | pin no. | function                                                                                                                                                                            |

|----------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BLANKN   | 0    | 84      | Active LOW, 3-state blanking output. BLANKN is asserted during vertical and horizontal blanking periods. At all other times, it is HIGH.                                            |

| DA       | 0    | 58      | Active HIGH, 3-state display active output. DA is LOW during the vertical retrace period. DA is in high impedance during the horizontal retrace period and HIGH at all other times. |

| M/SN     | 1    | 60      | Master/Slave input. The Master mode is selected when M/SN is HIGH.                                                                                                                  |

|          |      |         | Coprocessor handshake                                                                                                                                                               |

| CYREQN   | 1    | 107     | Active LOW cycle request input from coprocessor. When CYREQN is asserted, a coprocessor information transfer cycle is provoked.                                                     |

| CYACKN   | 0    | 111     | Active LOW cycle acknowledge output to the coprocessor. CYACKN is used for coprocessor handshaking.                                                                                 |

|          |      |         | Miscellaneous signals                                                                                                                                                               |

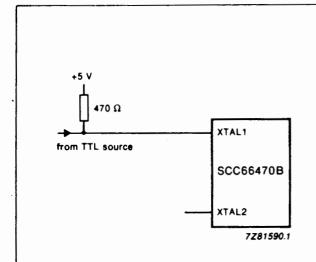

| XTAL1    |      | 123     | Crystal oscillator input. XTAL1 may also be used to input an external clock signal.                                                                                                 |

| XTAL2    | 0    | 2       | Crystal oscillator output.                                                                                                                                                          |

| RSTINN   |      | 59      | Active LOW Schmitt trigger RESET input. RSTINN is used to initiate a reset sequence and is pulled HIGH by an internal 30 $k\Omega$ pull-up resistor.                                |

| XT/2     | 0    | 122     | Xtal/2 clock output. Output frequency = f <sub>OSC</sub> /2                                                                                                                         |

| XT/4     | 0    | 121     | Xtal/4 clock output. Output frequency = f <sub>OSC</sub> /4                                                                                                                         |

| TST      | 1    | 61      | Test input. TST should be tied to VSS for normal operation.                                                                                                                         |

# Notes

- 1. All pins are TTL compatible except for XTAL1, XTAL2 and RSTINN which are CMOS compatible.

- 2. There are nine  $V_{DD}$  and nine  $V_{SS}$  pins. The following pins must be tied to  $V_{DD}$ : 15, 31, 48, 62, 79, 93, 99, 108, 124; the following pins must be tied to  $V_{SS}$ : 1, 17, 32, 46, 63, 77, 94, 100, 110.

# **FUNCTIONAL DESCRIPTION**

The SCC66470B performs the following functions:

- A. System Control: Integrates the necessary logic for a minimal system.

- B. Dynamic RAM Control: Direct drive for several types of DRAM.

- C. Display Control: On-chip timing chain, video address generator and shift register. A special reload mechanism permits the use of dynamic control words during display.

- Pixel Manipulation: On-chip logic optimized for image manipulation.

- E. Coprocessor Interface: On-chip interface which enables the SCC66470B to be used with a coprocessor or CPU.

#### A. SYSTEM CONTROL

The VSC performs the following 680XX system control functions:

# Reset and Halt Operations

The SCC66470B is reset when the RSTINN pin is released. The timing chain then counts 8 video frames before the HALTN and RSTOUTN are simultaneously released.

# **Memory Swapping**

After RSTINN is released, the VSC routes the first four 680XX accesses to the ROM (CSN must be asserted). After swapping, the ROM is decoded normally (180000H).

# **Address Decoding**

The VSC is connected to the system bus via 20 address lines. Thus, 2 M bytes (each word = 2 bytes) may be accessed via the VSC. Memory mapping depends on the type of DRAM used (64 K or 256 K) and on the synchronization mode (see Table 1).

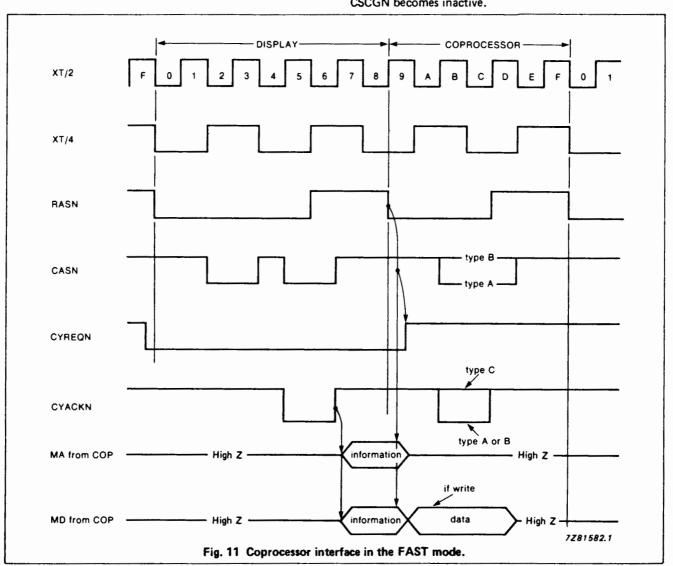

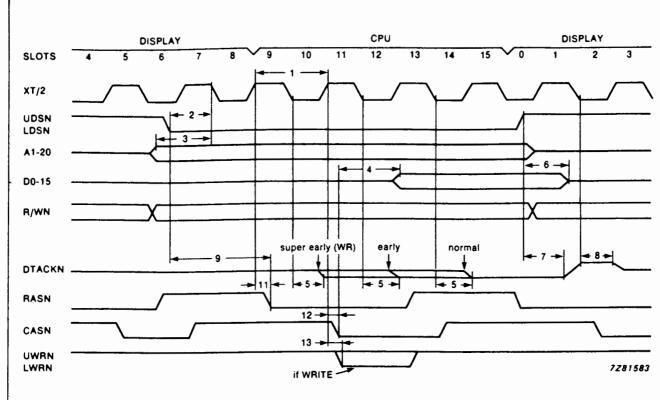

# **DTACKN** Generation

The SCC66470B generates the Data Acknowledge signal as follows:

- Access to DRAM is acknowledged as soon as it is certain that data will be available for the CPU.

DTACKN can be advanced by two clock periods using the ED bit in the CSR register.

- Access to internal registers is acknowledged immediatly after arbitration against a potential access from the coprocessor.

- Access to system ROM is ackowledged after approximately 16 clock periods. DTACKN will be advanced by 8 clock periods if the DD bit in the CSR register is set. This gives a maximum DTACKN delay of either 350 ns or 600 ns with a 30 MHz crystal.

- Access to system I/O devices (CSION pin) is acknowledged by the addressed device and not by the VSC.

Access to DRAM I/O (CCSION) is acknowledged in the same way as access to DRAM. The device is considered synchronous with accesses on the memory data bus.

## **Bus Error Generation**

The BERRN signal is asserted when the BE bit in the Control register CSR is set and when the selection is not acknowledged for at least one complete video line (approximately 64  $\mu$ s). The BE flag bit is then set in CSR. When the CPU reads the CSR status register, the BERRN pin and the BE flag are reset.

#### Interrupt Generation

The VSC generates interrupt requests to the CPU by asserting the INTN pin. The following conditions can generate an interrupt:

- The Dynamic Control Mechanism (DCA) fetches an interrupt instruction. Then, the IT1 bit of the CSR register is set.

- The pixel accelerator (PIXAC) code is reset by the coprocessor. Then, the IT2 bit of the CSR register is set.

The INTN pin, IT1 and IT2 are reset when the CPU reads the CSR register.

# **B. DRAM INTERFACE**

The SCC66470B has an on-chip Dynamic RAM controller which may be programmed for normal, page, nibble and video RAM devices.

# **Driving Modes**

The VSC can directly drive up to 16 memory devices. They may be arranged in one bank of 16 devices (64 K  $\times$  1 or 256 K  $\times$  1 DRAMS) on in several banks of four devices (64 K  $\times$  4 or 256 K  $\times$  4 DRAMS). The TD bit in the CSR register selects either 64 K or 256 K DRAMS.

# **DRAM** Access and Arbitration

The DRAM can be used as system memory and video memory. Thus, the CPU or coprocessor can access any portion of the entire memory space during active video display time. The DRAM can also be accessed by several masters and on-chip arbitration logic is implemented to provide each master with a guaranteed access time (timing window). The various masters are:

- The system bus (CPU or DMA cycles)

- The display

- ICA/DCA controller

- The DRAM refresh controller

- The coprocessor bus.

Table 1 Address Map

|                  | 256                   | i K                   | 64 K                  |                       |  |

|------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|

| ADDRESS          | MASTER OR<br>SLAVE TV | SLAVE DUAL            | MASTER OR<br>SLAVE TV | SLAVE DUAL            |  |

| 000000<br>01FFFF |                       |                       | BANK 1                |                       |  |

| 020000<br>03FFFF | BANK 1                | BANK1                 | BANK 2                |                       |  |

| 040000<br>05FFFF | BANKI                 | DAINT                 | BANK 3                |                       |  |

| 060000<br>07FFFF | ,                     |                       | BANK 4                |                       |  |

| 080000<br>09FFFF |                       |                       |                       | BANK 1                |  |

| 0A0000<br>0BFFFF | DANK 2                | DANK O                |                       | BANK 2                |  |

| 0C0000<br>0DFFFF | BANK 2                | BANK 2                |                       | BANK 3                |  |

| 0E0000<br>0FFFFF | -                     |                       |                       | BANK 4                |  |

| 100000<br>17FFFF | BANK 3                | BANK 3                |                       |                       |  |

| 180000<br>1FFBFF | SYSTEM ROM            |                       | SYSTEM ROM            |                       |  |

| 1FFC00<br>1FFF7F | SYSTEM I/O            | SYSTEM I/O            | SYSTEM I/O            | SYSTEM I/O            |  |

| 1FFF80<br>1FFFBF | DRAM I/O              |                       | DRAM I/O              |                       |  |

| 1FFFC0<br>1FFFDF |                       | INTERNAL<br>REGISTERS |                       | INTERNAL<br>REGISTERS |  |

| 1FFFE0<br>1FFFFF | INTERNAL<br>REGISTERS |                       | INTERNAL<br>REGISTERS |                       |  |

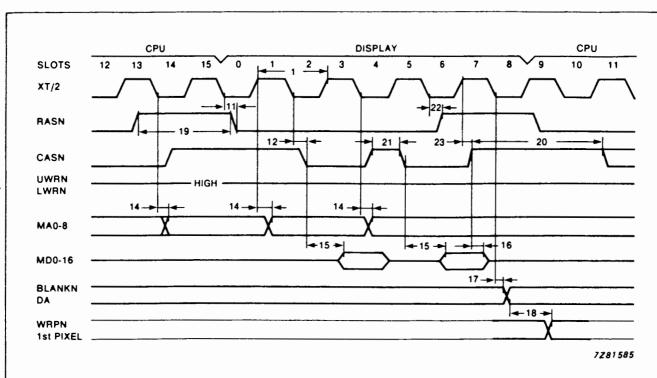

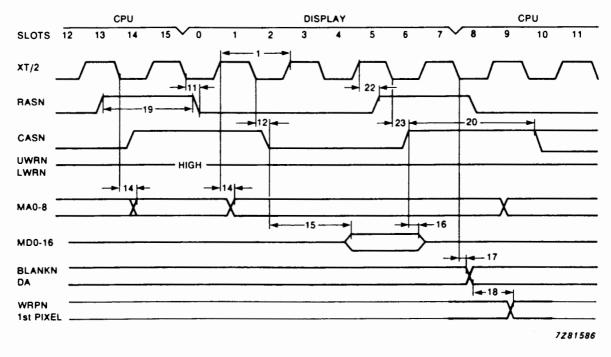

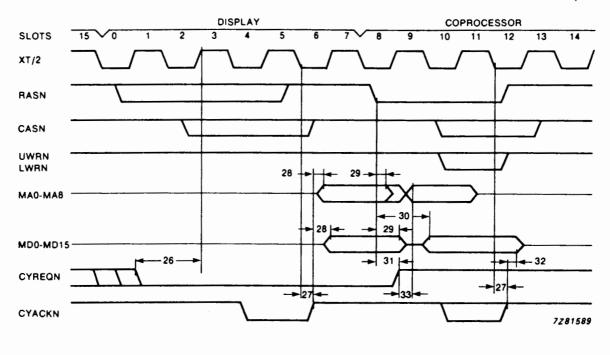

DRAM access cycles contain pairs of timing windows. Each cycle has a duration of 16 XTAL periods. The first window is used by video related functions (Display or ICA/DCA controllers) and the DRAM refresh controller. The second window is available for DRAM accesses from the system bus (CPU or DMA cycles) or from the coprocessor bus. When the video and refresh functions are inactive, DRAM accesses are free-running with no windows so that a system or coprocessor access can occur at any time and the appropriate RASN and CASN signals are asserted.

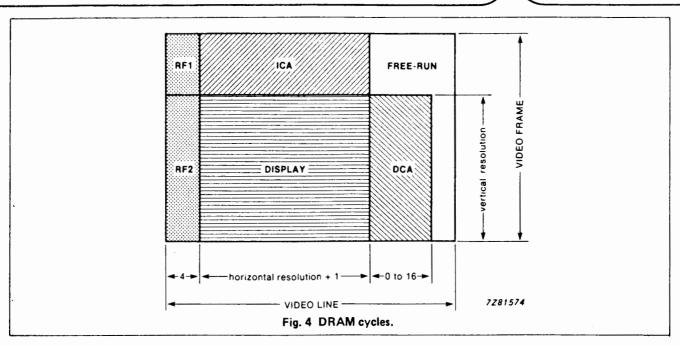

Fig. 4 shows the number of cycles related to the time domain of a complete video frame. Note that:

- RF1 and RF2 are refresh cycles

- ICA and DCA only exist when they are enabled

- RF2 only exists in the LOGICAL SCREEN mode

- If the display is not enabled, all areas other than the refresh areas are FREE-RUN

- In Dual-port mode, all display windows other than the first display window of each line (1 window) are available to the system bus.

DR.

0

# **DRAM Timing**

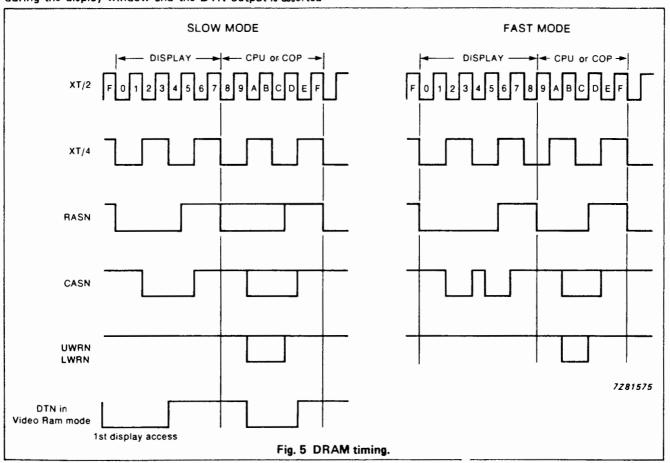

The SCC66470B can use normal, nibble, page or dual-port video DRAM types. Two bits in the CSR register (DM1 and DM2) are used to select the DRAM type. In the page and nibble modes, DRAM timing is in the FAST mode. In the FAST mode, two display fetches are performed in the same cycle. In the nibble mode, the LSB and MSB address lines may be switched externally. In the dual port video RAM mode, the CPU has twice as much access time available during the display window and the DTN output is asserted

at the beginning of each video line. Fig. 5 shows cycle windows in the display area in both the SLOW and FAST modes.

# **DRAM Deselect**

During a RESET, a memory bank will be deselected if its corresponding CASN pin is grounded and no DTACKN will be generated for this bank. To select the memory bank, a pull-up resistor is required.

# C. DISPLAY CONTROL

Several pre-programmed display modes may be selected and the VSC contains a Video Start address register to locate the video display within the first 1 M Byte of the DRAM address space. The display logic reads a word from the video display area and then serializes it either nibble by nibble (4 bits per pixel) or byte by byte (8 bits per pixel).

#### Resolution

# Horizontal resolution

Table 2 shows the horizontal resolution as set by bits CF1, CF2, SS and CM in the DCR register for the FAST mode (set by bits DM1 and DM2 in the CSR register). If the SLOW mode is selected or if the Double Frequency mode is active, then the horizontal resolution shown in Table 2 is halved.

#### Vertical resolution

Table 3 shows the vertical resolution as set by bits FD and SS in the DCR register for non-interlaced and interlaced field repeat modes. For double frequency and normal interlaced modes, the vertical resolution shown in Table 3 is doubled.

## Reduced and Full Screens

In the Full Screen mode (SS = 1), the picture covers the entire TV screen. In the Reduced Screen mode (SS = 0), a border of the programmable colour is displayed on the top, bottom, left and right parts of the visible screen. The border colour register (BCR) is 8 bits wide. In the 8 bits per pixel mode, 256 colours are possible and, in the 4 bits per pixel mode, 16 colours are possible.

# Physical and Logical Screen

The SCC6470B can organize the display memory in either of two ways: logical screen mode or physical screen mode. The logical screen mode is selected when the LS bit of the DCR register is set and the physical screen mode is selected when LS is reset. The Video Start Register (VSR) points to the beginning of the physical display.

In the logical screen mode, the bit map width is 512 bytes. The 9 least significant bits of the VSR register are reloaded to the beginning of each display line. A horizontal wraparound will occur if the VSR points too far to the right of a memory line.

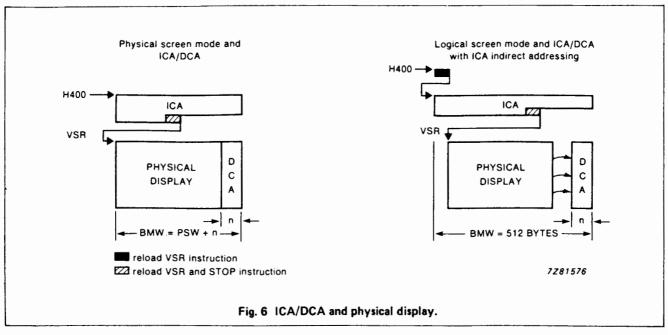

In the physical screen mode, the memory line width and the bit map width are the same as the display line width. The first pixel of a line immediately follows the last pixel of the previous line. In the physical screen mode, interlacing is not permitted and dual-port video RAM can not be accessed. With a 27.5 MHz oscillator, in full screen mode, the bit map is 384 pixels wide even if the display is 360 pixels wide.

# Image Control Area (ICA) and Dynamic Control Area (DCA) Mechanisms.

The SCC66470B enables control information to be fetched during vertical and horizontal retrace periods. This feature is enabled via the IC and DC bits in the DCR register. The VSR register is used as a dynamic ICA/DCA pointer.

#### ICA Mechanisms

This mechanism consists of fetching Long Word instructions during the vertical retrace period. The ICA pointer is either 400H or 80400H at the beginning of the vertical retrace period (see Table 4). At least 500 instructions can be fetched in the ICA.

#### DCA Mechanism

In this case, the instruction fetch occurs during the horizontal retrace period. The DCA is located next to the display memory (see Fig. 6). In the physical screen mode, the bit map width is thus increased by the number of possible DCA fetches (see Table 5).

The number of possible fetches depends on the mode (see Table 5). This number is halved for the SLOW mode.

# Screen Management

## Screens and Sub Screens

The VSR register points to a display line in the 1 M Byte display RAM area. During the execution of a reload VSR instruction, the VSR register functions as an ICA/DCA pointer. The reload VSR and STOP instruction stops the ICA/DCA mechanism and facilitates a new screen (ICA) or subscreen (DCA). This permits vertical rolling and vertical split screens.

# Horizontal rolling

The 2 least significant bits of the VSR should be logic 0 since the 20 bit video start address (held in VSR and the four least significant bits of the DCR register) must be Long Word aligned. However, in the logical, reduced screen and fast modes, horizontal byte rolling in screen or subscreen is possible by using these 2 VSR bits to specify a 2 byte offset.

# Notes to Fig. 6:

- 1. BMW: Bit Map Width.

- 2. PSW: Physical Display Width.

- 3. n: The DCA width is 16 or 64 in the logical screen mode. In the physical screen mode, the DCA width is 16, 32 or 64.

Table 2 Horizontal resolution

|     |     |     | fosc    | number of | pixels/line | active line |

|-----|-----|-----|---------|-----------|-------------|-------------|

| CF1 | CF2 | SS  | (MHz)   | CM = 1    | CM = 0      | (μs)        |

| 0   | 0   | 0   | 19.6608 | 448       | 224         | 45.6        |

| 0   | 0   | 1   | 19.6608 | 512       | 256         | 52          |

| 0   | 1   | 0   | 24      | 512       | 256         | 42.6        |

| 0   | 1   | 1   | 24      | 640       | 320         | 53.3        |

| 1   | 0   | 0   | 27.5    | 640       | 320         | 46.5        |

| 1   | 0   | 1 1 | 27.5    | 720       | 360         | 52.4        |

| 1   | 1   | 0   | 30      | 640       | 320         | 42.6        |

| 1   | 1   | 1   | 30      | 768       | 384         | 51.2        |

Table 3 Vertical resolution

| FD<br>0 | SS<br>O | number of lines | frame duration<br>(ms) | image frequency<br>(Hz) |

|---------|---------|-----------------|------------------------|-------------------------|

| 0       | 0       | 250             | 16                     | 50                      |

| 0       | 1       | 280             | 16                     | 50                      |

| 1       | 0       | 210             | 13.4                   | 60                      |

| 1       | 1       | 240             | 15.3                   | 60                      |

Table 4 ICA pointer

|             | 25                | 6 K                | 64 K   |            |

|-------------|-------------------|--------------------|--------|------------|

|             | bank 1<br>enabled | bank 1<br>disabled | master | slave dual |

| ICA pointer | H400              | H80400             | H400   | H80400     |

Table 5 Number of DCA fetches

| IC | DC | double frequency<br>SM.DF | SS | CF1 | CF2 | DCA (in bytes)        |

|----|----|---------------------------|----|-----|-----|-----------------------|

| X  | 0  | ×                         | ×  | X   | ×   | 0                     |

| 0  | 1  | ×                         | ×  | X   | ×   | 16 (reduced DCA mode) |

| 1  | 1  | 1                         | x  | X   | ×   | 16                    |

| 1  | 1  | 0                         | 0  | X   | ×   | 64                    |

| 1  | 1  | 0                         | 1  | 0   | ×   | 32                    |

| 1  | 1  | 0                         | 1  | 1   | 0   | 32                    |

| 1  | 1  | 0                         | 1  | 1   | 1   | 64                    |

Note: ICA/DCA instructions are Long Word Aligned and Long Word Wide. In the SLOW mode, the number of fetches is halved. X = don't care.

Table 6 ICA/DCA instruction list

| code                                       | instruction         | description                                                                                                                                                                                                                                      |

|--------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00XX XXXX XXXX XXXX                        | STOP                | Stop the control sequence. The instruction fetches are then stopped.                                                                                                                                                                             |

| 0100 XXXX XXXX PPPP<br>PPPP PPPP PPPP      | RELOAD VSR          | Reload the VSR and the video address counter with the specified pointer. The following fetches will use the new value. The VSR is considered as an ICA or DCA pointer.                                                                           |

| 0101 XXXX XXXX PPPP<br>PPPP PPPP PPPP PPPP | RELOAD VSR and STOP | Reload the VSR with the specified pointer and then stop the control fetches.                                                                                                                                                                     |

| 0110 XXXX XXXX XXXX<br>XXXX XXXX XXXX XXXX | INTERRUPT           | Generate an interrupt request to the CPU and set CSR bit, IT1.                                                                                                                                                                                   |

| 0111 XXXX CCCC CCCC<br>XXXX XXXX XXXX XXXX | RELOAD BORDER       | Reload border colour register with specified colour immediately.                                                                                                                                                                                 |

| 1888 BBBB BBBB BBBB<br>BBBB BBBB BBBB      | BEP CONTROL         | Back-End Processor control. The WRPN signal goes LOW. The 32 bits are passed via the video output port (V7 – V0) to the BEP without alteration.  The information is always output in groups of 8 bits (equivalent to the 8 bits per pixel mode). |

# Notes to Table 6:

- 1. X = don't care.

- 2. P = ICA/DCA pointer data.

- 3. C = border colour data.

- 4. B = Back-End Processor information.

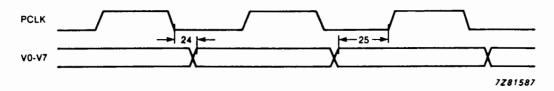

# **Pixel Output**

The internal shift register outputs pixels as follows: Memory word, MD15 - MD0 (15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0), is serialized to either:

15, 14, 13, 12, 11, 10, 9, 8 and then 7, 6, 5, 4, 3, 2, 1, 0 (8 bits per pixel) or

15, 14, 13, 12 and then 11, 10, 9, 8, then 7, 6, 5, 4, then 3, 2, 1, 0 (4 bits per pixel).

Table 7 shows the number of bits per pixel for various PCLK frequencies. If the BLANKN pin is reset (retrace period) and if WRPN is inactive, the pixel port is forced to logic 0.

Table 7 PCLK frequency and the number of bits per pixel

| WRPN | СМ | timing mode | bits/pixel | PCLK<br>frequency |

|------|----|-------------|------------|-------------------|

| 1    | 0  | fast        | 8          | XTAL/4            |

| 1    | 1  | fast        | 4          | XTAL/2            |

| 1    | X  | slow        | 4          | XTAL/4            |

| 0    | X  | fast        | 8          | XTAL/4            |

| 0    | X  | slow        | 8          | XTAL/8            |

X = don't care.

# Video Synchronization

The SCC66470B can operate in the following modes:

Master mode: HSYNCN and VSYNCN are both

outputs

Slave TV mode: HSYNCN is an output and VSYNCN

is an input

• Slave Dual mode: HSYNCN and VSYNCN are both

inputs.

The VSC is initialized when the DE bit in the DCR register is reset via the CSYNCN and MSN pins.

**Table 8 Synchronization**

| MSN | CSYNCN pin (DE = 0) | synchronization mode |

|-----|---------------------|----------------------|

| 1   | X                   | Master               |

| 0   | 1 (no pull down)    | Slave TV             |

| 0   | 0 (10 kΩ pull down) | Slave Dual           |

X = don't care.

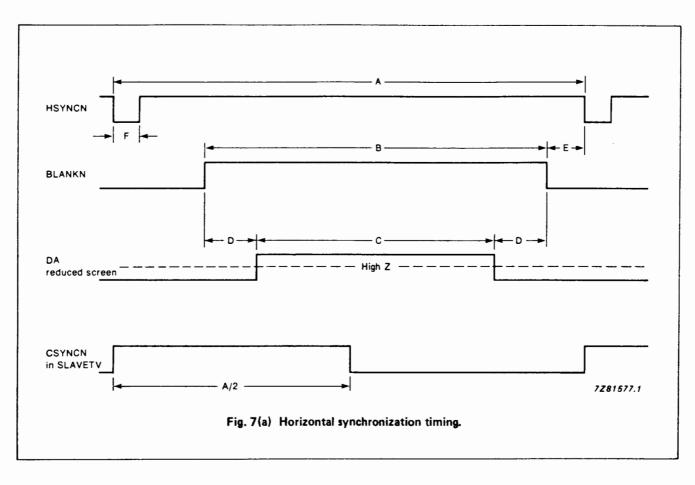

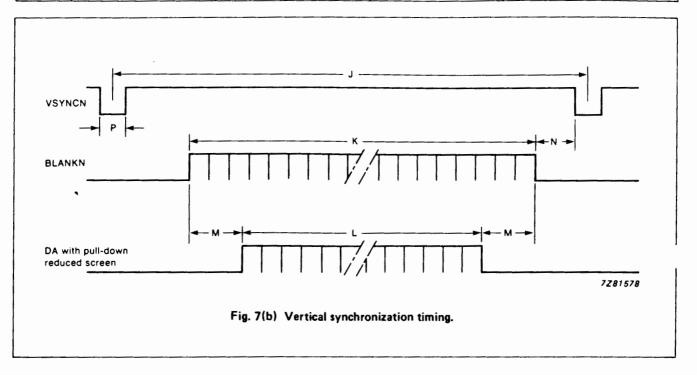

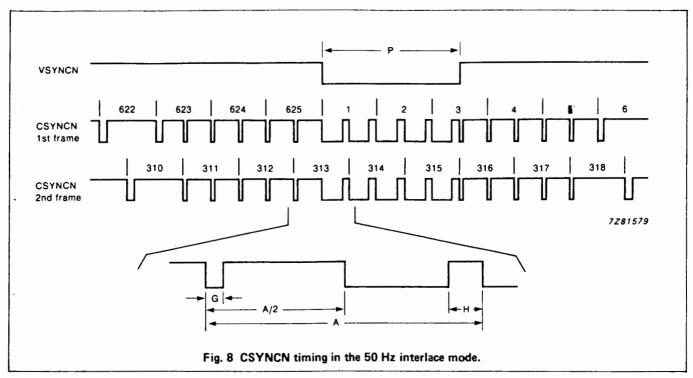

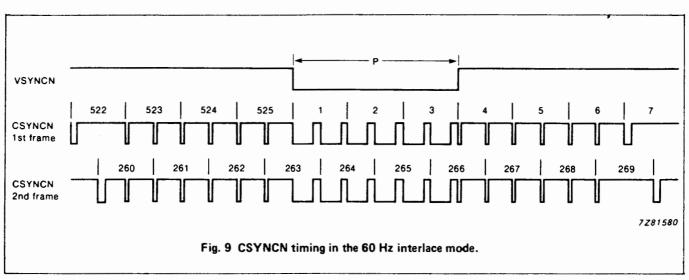

Figures 7(a), 7(b), 8 and 9 show the HSYNCN, CSYNCN, BLANKN and DA timing in the Master and reduced screen modes.

Table 9 Horizontal synchronization timing

|   | 19.660 | 08 MHz | 24 N   | 24 MHz 27.5 |        | 5 MHz | 30     | MHz   |

|---|--------|--------|--------|-------------|--------|-------|--------|-------|

|   | cycles | μs     | cycles | μs          | cycles | μs    | cycles | μs    |

| A | 80     | 65.1   | 96     | 64          | 110    | 64    | 120    | 64    |

| В | 64     | 52.08  | 80     | 53.33       | 90     | 52.36 | 96     | 51.2  |

| С | 56     | 45.47  | 64     | 42.67       | 80     | 46.55 | 80     | 42.67 |

| D | 4      | 3.26   | 8      | 5.33        | 5      | 2.91  | 8      | 4.27  |

| E | 2      | 1.63   | 1      | 0.67        | 2      | 1.16  | 3      | 1.6   |

| F | 6      | 4.88   | 7      | 4.67        | 8      | 4.65  | 9      | 4.8   |

| G | 3      | 2.44   | 3      | 2           | 4      | 2.33  | 4      | 2.13  |

| Н | 6      | 4.88   | 7      | 4.67        | 8      | 4.65  | 9      | 4.8   |

Table 10 Vertical synchronization timing

|       |                       |                                           |                                                               | erlace 60 Hz non interlace                                                        |                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                | nteriace                                                                                                                                                                                                                                           |

|-------|-----------------------|-------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lines | ms                    | lines                                     | ms                                                            | lines                                                                             | ms                                                                                                                                                                                                                                                  | lines                                                                                                                                                                                                          | ms                                                                                                                                                                                                                                                 |

| 312   | 19.97                 | 312.5                                     | 20                                                            | 262                                                                               | 16.77                                                                                                                                                                                                                                               | 262.5                                                                                                                                                                                                          | 16.8                                                                                                                                                                                                                                               |

| 280   | 17.92                 | 280                                       | 17.92                                                         | 240                                                                               | 15.36                                                                                                                                                                                                                                               | 240                                                                                                                                                                                                            | 15.36                                                                                                                                                                                                                                              |

| 250   | 16                    | 250                                       | 16                                                            | 210                                                                               | 12.44                                                                                                                                                                                                                                               | 210                                                                                                                                                                                                            | 13.44                                                                                                                                                                                                                                              |

| 15    | 0.96                  | 15                                        | 0.96                                                          | 15                                                                                | 0.96                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                             | 0.96                                                                                                                                                                                                                                               |

| 6     | 0.384                 | 6 or 6.5                                  | 0.416                                                         | 4                                                                                 | 0.256                                                                                                                                                                                                                                               | 4 or 4.5                                                                                                                                                                                                       | 0.288                                                                                                                                                                                                                                              |

| 2.5   | 0.16                  | 2.5                                       | 0.16                                                          | 3                                                                                 | 0.192                                                                                                                                                                                                                                               | 3                                                                                                                                                                                                              | 0.192                                                                                                                                                                                                                                              |

|       | 280<br>250<br>15<br>6 | 280 17.92<br>250 16<br>15 0.96<br>6 0.384 | 280 17.92 280<br>250 16 250<br>15 0.96 15<br>6 0.384 6 or 6.5 | 280 17.92 280 17.92<br>250 16 250 16<br>15 0.96 15 0.96<br>6 0.384 6 or 6.5 0.416 | 280         17.92         280         17.92         240           250         16         250         16         210           15         0.96         15         0.96         15           6         0.384         6 or 6.5         0.416         4 | 280     17.92     280     17.92     240     15.36       250     16     250     16     210     12.44       15     0.96     15     0.96     15     0.96       6     0.384     6 or 6.5     0.416     4     0.256 | 280     17.92     280     17.92     240     15.36     240       250     16     250     16     210     12.44     210       15     0.96     15     0.96     15     0.96     15       6     0.384     6 or 6.5     0.416     4     0.256     4 or 4.5 |

# Frame Grabbing

When the frame grabbing bit (FG) in the DCR register is set, the SCC66470B completes the current frame before the grabbing period starts. The grabbing period consists of either one frame or two frames (interlaced mode). During this period, UWRN and LWRN are continually asserted, the DRAM can not be accessed and the MD bus is in the input mode. The CPU can poll the FG bit in the CSR register to detect the end of the grabbing period.

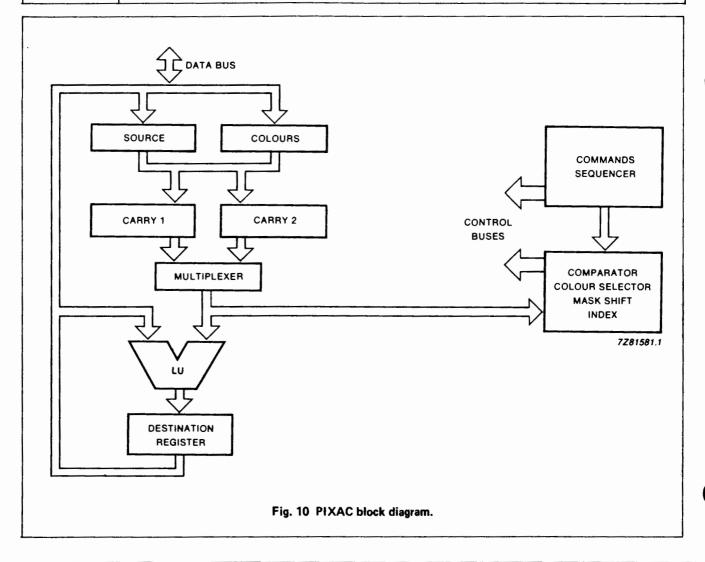

# D. PIXEL ACCELERATOR LOGIC

The SCC66470B has on-chip pixel accelerator logic (PIXAC) to speed up the manipulation of pixel contents in memory. The PIXAC may be used in conjunction with either the CPU or the coprocessor. The ten PIXAC operations are explained in Table 11.

In addition, the PIXAC alligns source words onto destination words, masks destination pixels and magnifies or shrinks with a factor of 2 (COPY, PATCH and COLOUR). When the IPA pin is HIGH, the system bus is disconnected internally and the PIXAC is directly connected to the DRAM bus in order to speed up data transfers. The PIXAC command register (PCR) defines the implicit PIXAC register.

**Table 11 PIXAC Operations**

| operation | description                                                                                                                                                                                                                                                                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COPY      | Source pixels are copied into destination pixels.                                                                                                                                                                                                                                                                                                         |

| PATCH     | Source pixels other than transparent source pixels are copied into destination pixels.                                                                                                                                                                                                                                                                    |

| EXCHANGE  | Source pixels are exchanged with destination pixels.                                                                                                                                                                                                                                                                                                      |

| SWAP      | Source pixels other than transparent source pixels are exchanged with destination pixels.                                                                                                                                                                                                                                                                 |

| COLOUR 1  | For non-transparent source pixels, destination pixels are changed to the current foreground colour.  For transparent source pixels, destination pixels are not affected.                                                                                                                                                                                  |

| COLOUR 2  | For non-transparent source pixels, destination pixels are changed to the current foreground colour. For transparent source pixels, destination pixels are changed to the current background colour.                                                                                                                                                       |

| BCOLOUR 1 | Source word bits are extended into pixels via the pixel path. For source bits that are set, destination pixels are changed to the foreground colour. For source bits that are reset, destination pixels are not affected. An index register, which is automatically incremented, points to the source nibble to be processed.                             |

| BCOLOUR 2 | Source word bits are extended into pixels via the pixel path. For source bits that are set, destination pixels are changed to the foreground colour. For source bits that are reset, destination pixels are changed to the current background colour. An index register, which is automatically incremented, points to the source nibble to be processed. |

| COMPARE   | Source pixels are compared with transparent colour. The result is stored in the most significant nibble of the B register.                                                                                                                                                                                                                                |

| COMPACT   | Source pixels are compared with transparent colour. The result of each test is stored in a nibble pointed to by an index register. The index register is automatically incremented.                                                                                                                                                                       |

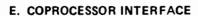

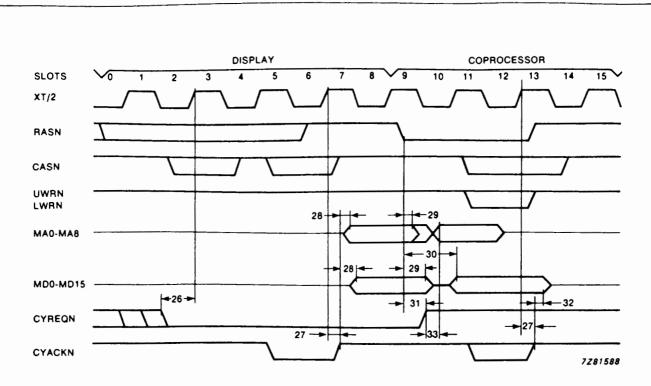

The SCC66470B contains an interface which enables another CPU or coprocessor to access the DRAM, PIXAC and CSR registers. A coprocessor may be connected to the VSC via the Memory Data (MD) bus, the Memory Address (MA) bus and the Control lines. Handshake pins CYREQN, CYACKN and RASN are provided to request and acknowledge data exchange between the VSC and a coprocessor.

## Interface

Three types of exchange are possible. These are:

Type A: an exchange between the coprocessor memory Type B: an exchange between the coprocessor and the PIXAC

Type C: an exchange between memory and the PIXAC registers (controlled by the coprocessor).

An exchange takes place as follows:

- . 1. The coprocessor asserts CYREQN.

- 2. On the rising edge of CYACKN, the coprocessor supplies address and control information on the MA and MD buses.

- On the falling edge of RASN, the MA bus and CYREQN must be released. The data bus (MD) must be released for a Type C exchange or a read cycle. For a Type A exchange, a Type B exchange or a write cycle, the data bus must contain the written data.

- 4. For a Type A or Type B exchange, the rising edge of a second CYACKN pulse indicates that the exchange is complete and that the data bus must be released for a write cycle.

Information transfer between the coprocessor and the MA and MD buses is shown in Table 12.

A1 to A20 are the coprocessor address lines (word address). R/WNh and R/WNI are the higher and lower byte write signals for the DRAM.

SELA or SELB are asserted during a type C exchange and correspond to direct addressing of the PIXAC.

#### Character ROM Access

Setting the CG bit in the CSR register enables a Type C exchange with ROM. The ROM must reside in memory Bank 3 and ROM addresses must be latched after the first CAS3N assertion. ROM data is output enabled by the CSCGN signal. The exchange will be complete when CSCGN becomes inactive.

Table 12 Coprocessor data exchange

|                         |                      | 256 K DRAM |          | 64 K                 | DRA <b>M</b> |

|-------------------------|----------------------|------------|----------|----------------------|--------------|

| coprocessor information | normal<br>and nibble | page       | VRAM     | normal<br>and nibble | page         |

| A1                      | MA0 R                | MD0 C      | MD0 C    | MAO R                | MD0 C        |

| A2                      | MA1 R                | MA1 R      | MD1 C    | MA1 R                | MA1 R        |

| A3                      | MA2 R                | MA2 R      | MD2 C    | MA2 R                | MA2 R        |

| A4                      | MA3 R                | MA3 R      | MD3 C    | MA3 R                | MA3 R        |

| A5                      | MA4 R                | MA4 R      | MD4 C    | MA4 R                | MA4 R        |

| A6                      | MA5 R                | MA5 R      | MD5 C    | MA5 R                | MA5 C        |

| A7                      | MA6 R                | MA6 R      | MD6 C    | MA6 R                | MA6 R        |

| A8                      | MA7 R                | MA7 R      | MD7 C    | MA7 R                | MA7 R        |

| A9                      | MA8 R                | MA8 R      | MD8 C    | MA8 C                | MA8 C        |

| A10                     | MD0 C                | MAO R      | MA0 R    | MD0 C                | MA0 R        |

| A11                     | MD1 C                | MD1 C      | MA1 R    | MD1 C                | MD1 C        |

| A12                     | MD2 C                | MD2 C      | MA2 R    | MD2 C                | MD2 C        |

| A13                     | MD3 C                | MD3 C      | MA3 R    | MD3 C                | MD3 C        |

| A14                     | MD4 C                | MD4 C      | MA4 R    | MD4 C                | MD4 C        |

| A15                     | MD5 C                | MD5 C      | MA5 R    | MD5 C                | MD5 C        |

| A16                     | MD6 C                | MD6 C      | MA6 R    | MD6 C                | MD6 C        |

| A17                     | MD7 C                | MD7 C      | MA7 R    | MD7 CAS              | MD7 CAS      |

| A18                     | MD8 C                | MD8 C      | MA8 R    | MD8 CAS              | MD8 CAS      |

| A19                     | MD9 CAS              | MD9 CAS    | MD9 CAS  | not                  | used         |

| A20                     | MD10 CAS             | MD10 CAS   | MD10 CAS | not                  | used         |

| SELA                    | MD12                 | MD12       | MD12     | MD12                 | MD12         |

| SELB                    | MD13                 | MD13       | MD13     | MD13                 | MD13         |

| R/WNI                   | MD14                 | MD14       | MD14     | MD14                 | MD14         |

| R/WNh                   | MD15                 | MD15       | MD15     | MD15                 | MD15         |

# **REGISTER DESCRIPTION**

The SCC66470B registers are described in Table 13.

Table 13 VSC registers

| register | address |     |    |     |     |     |     |     | ŧ   | it num | ber |     |    |    |     |     |     |    |

|----------|---------|-----|----|-----|-----|-----|-----|-----|-----|--------|-----|-----|----|----|-----|-----|-----|----|

| name     | (Hex)   | R/W | 15 | 14  | 13  | 12  | 11  | 10  | 9   | 8      | 7   | 6   | 5  | 4  | 3   | 2   | 1   | 0  |

| CSR*     | 1FFFE0  | w   | x  | x   | ×   | x   | x   | x   | x   | x      | DM1 | DM2 | TD | CG | DD  | ED  | 0   | BE |

| CSR*     | 1FFFE0  | R   | Х  | X   | X   | X   | Х   | X   | X   | X      | DA  | FG  | X  | Х  | X   | IT2 | IT1 | BE |

| DCR      | 1FFFE2  | W   | DE | CF1 | CF2 | FD  | SM  | SS  | LS  | CM     | FG  | DF  | IC | DC | dt  | dt  | dt  | dt |

| VSR      | 1FFFE4  | W   | dt | dt  | dt  | dt  | dt  | dt  | dt  | dt     | dt  | dt  | dt | dt | dt  | dt  | dt  | dt |

| BCR*     | 1FFFE6  | W   | Х  | X   | X   | X   | X   | X   | X   | X      | dt  | dt  | dt | dt | dt  | dt  | dt  | dt |

| SWM      | 1FFFEC  | W   | dt | dt  | dt  | dt  | dt  | dt  | dt  | dt     | X   | X   | X  | Х  | X   | X   | X   | Х  |

| STM*     | 1FFFEE  | W   | X  | X   | X   | X   | X   | X   | X   | X      | dt  | dt  | dt | dt | dt  | dt  | dt  | dt |

| Α        | 1FFFF0  | W   | dt | dt  | dt  | dt  | dt  | dt  | dt  | dt     | dt  | dt  | dt | dt | dt  | dt  | dt  | dt |

| В        | 1FFFF2  | R/W | dt | dt  | dt  | dt  | dt  | dt  | dt  | dt     | dt  | dt  | dt | dt | dt  | dt  | dt  | dt |

| PCR      | 1FFFF4  | W   | 4N | COL | ENC | CPY | CMP | RTL | SHK | ZOM    | dt  | dt  | dt | dt | INV | BIT | TT  | 0  |

| MASK*    | 1FFFF6  | W   | X  | X   | X   | Х   | Х   | X   | X   | X      | X   | X   | X  | X  | dt  | dt  | dt  | dt |

| SHIFT*   | 1FFFF8  | W   | X  | X   | X   | X   | X   | X   | dt  | dt     | X   | X   | X  | X  | X   | X   | X   | X  |

| INDEX*   | 1FFFFA  | W   | X  | X   | X   | X   | X   | Х   | X   | X      | X   | X   | X  | X  | X   | X   | dt  | dt |

| FC*      | 1FFFFC  | W   | dt | dt  | dt  | dt  | dt  | dt  | dt  | dt     | X   | X   | X  | X  | X   | X   | Х   | Х  |

| BC*      | 1FFFFC  | W   | Х  | X   | Х   | X   | X   | Х   | X   | X      | dt  | dt  | dt | dt | dt  | dt  | dt  | dt |

| TC*      | 1FFFFE  | W   | dt | dt  | dt  | dt  | dt  | dt  | dt  | dt     | X   | Х   | X  | X  | ×   | Х   | X   | Х  |

# Where:

dt = data.

X = don't care

= byte addressable.

# SYSTEM AND DISPLAY ORIENTED REGISTERS

# The Control and Status Register, CSR

The CSR register controls the system related functions of the SCC66470B. When written to, it functions as a CONTROL register. When read, its acts as a STATUS register. It is reset to zero during the initialization sequence.

| symbol | function                                                                                                                                                                                                                                                                                                                                                       |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | Control Register (write operations)                                                                                                                                                                                                                                                                                                                            |

| DM1    | DRAM access mode control bits. Four configurations may be selected as follows:                                                                                                                                                                                                                                                                                 |

| DM2    | DM1   DM2   Timing Speed   DRAM Mode                                                                                                                                                                                                                                                                                                                           |

|        | 0 0 SLOW Mode Normal Mode                                                                                                                                                                                                                                                                                                                                      |

|        | 0 1 FAST Mode Page Mode                                                                                                                                                                                                                                                                                                                                        |

|        | 1 0 FAST Mode Nibble Mode                                                                                                                                                                                                                                                                                                                                      |

|        | 1                                                                                                                                                                                                                                                                                                                                                              |

| TD     | DRAM type (0 to 64 K devices or 1 to 256 K devices)                                                                                                                                                                                                                                                                                                            |

| CG     | Enables the character generator mode when set. When this mode is enabled, the timing of the CAS3N and CSCGN signals becomes ROM compatible for a coprocessor access.                                                                                                                                                                                           |

| DD     | ROM data acknowledge delay. When DD is set, the DTACK delay changes from approximately 16 clock periods to 8 clock periods.                                                                                                                                                                                                                                    |

| ED     | Early DTACK. When ED is set, data will be acknowledged (DTACK asserted) when the data becomes available on the system bus and an early DTACK will be generated 2 slots (66 ns with a 30 MHz oscillator) before the data is valid.                                                                                                                              |

| BE     | Bus error enable. When BE is set, the watchdog timer is activated and a BERR is generated.                                                                                                                                                                                                                                                                     |

|        | Status register (read operations)                                                                                                                                                                                                                                                                                                                              |

| DA     | Vertical display active. The DA bit is set when the display controller is fetching information from the video memory. It is not affected by a horizontal retrace.                                                                                                                                                                                              |

| FG     | This bit is set when frame grabbing is enabled by setting the FG bit in the DCR register. It is reset at the end of the frame grabbing period which has a duration of either one frame or two frames (interlaced mode).                                                                                                                                        |

| IT1    | IT1 can be set by the DCA mechanism to generate an interrupt request to the CPU. The INTN pin will go LOW simultaneously. The IT1 bit is automatically reset and the INTN output is automatically deactivated when the CPU reads the status register.                                                                                                          |

| IT2    | IT2 can be set by clearing bits 11 to 14 of the PIXAC command register (PCR). This action tells the CPU that the PIXAC is free and generates an interrupt request by asserting the INTN output. INTN is automatically reset when the CPU reads the status register or when one or more of the four bits in the PCR register (bits 11 to 14) is set to logic 1. |

| 8E     | This bit is set when a BUS ERROR condition has been generated by the watchdog timer. BE is automatically reset when the CPU reads the status register.                                                                                                                                                                                                         |

# The Display Command Register, DCR

The Display Command Register (DCR) contains the four most significant bits of the Video start address and the display control bits. The 12 bits are reset to zero during the reset sequence.

| symbol     | function                                                                                                                                                                                                                                               |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DE         | When set, the display enable bit enables the display controller.                                                                                                                                                                                       |

| CF1        | These bits must be loaded with a number which corresponds to the oscillator in use as follows:                                                                                                                                                         |

| CF2        | CF1   CF2   oscillator frequency                                                                                                                                                                                                                       |

|            | 0 0 19.6608 MHz or 20 MHz                                                                                                                                                                                                                              |

|            | 0   1   24 MHz<br>1   0   28.5 MHz                                                                                                                                                                                                                     |

|            | 1 1 30 MHz                                                                                                                                                                                                                                             |

| FD         | Frame duration control. When FD is set, the scan frequency is 60 Hz and when FD is reset, the scan frequency is 50 Hz.                                                                                                                                 |

| SM         | These two bits select the scan mode. Four scan modes may be selected as follows:                                                                                                                                                                       |

| DF         | SM DF scan mode                                                                                                                                                                                                                                        |

|            | 0 0 Non-interlaced                                                                                                                                                                                                                                     |

|            | 0 1 Double frequency (not possible with 20 MHz oscillator) 1 0 Interlaced                                                                                                                                                                              |

|            | 1 1 Interlaced field repeat                                                                                                                                                                                                                            |

|            | <ul> <li>Double frequency mode: the horizontal frequency is doubled and the vertical frequency is not<br/>affected. In this mode, horizontal resolution is halved and the vertical resolution is twice that<br/>of the non-interlaced mode.</li> </ul> |

|            | <ul> <li>Interlaced mode: two interleaved frames (one odd, one even) are displayed. The VSC automatically jumps from line n to line n + 2 in the same frame. This is not possible in the physical screen.</li> </ul>                                   |

|            | <ul> <li>Interlaced field repeat mode: two identical interleaved frames are displayed.</li> </ul>                                                                                                                                                      |

| SS         | Screen Size control. When SS is set, a full screen display is generated. When SS is reset, a display with borders is generated.                                                                                                                        |

| LS         | Logical Screen select. LS selects either a Logical Screen (LS = 1) or a Physical Screen (LS = 0). A Logical Screen requires 512 bytes per video line regardless of the status of CF1 and CF2.                                                          |

| СМ         | Colour Mode select. When CM is set, the 4 bits per pixel mode is selected. When CM is reset, the 8 bits per pixel mode is selected.                                                                                                                    |

| FG         | Frame Grabbing enable. Setting FG provokes frame grabbing during the next frame (or during the next 2 frames in the interlace mode). It is automatically reset after the grabbing operation. FG may be read from the CSR status register.              |

| IC         | IC and DC select various mechanisms as follows:                                                                                                                                                                                                        |

| DC         | IC DC mechanism                                                                                                                                                                                                                                        |

|            | 0 0 ICA and DCA inactive<br>0 1 ICA active, Reduced DCA Mode (DCA size = 16 bytes)                                                                                                                                                                     |

|            | 1 0 ICA active, Reduced DCA Mode (DCA Size = 10 bytes)                                                                                                                                                                                                 |

|            | 1 1 ICA active, DCA active (DCA size = 64 bytes)                                                                                                                                                                                                       |

| A16 to A19 | Four most significant bits of the Video Start Address. These four bits are used in conjunction with the VSR register.                                                                                                                                  |

# The Video Start Register, VSR